SLWU087E november 2013 – june 2023

- 1

- High Speed Data Converter Pro GUI

- Trademarks

- 1 Introduction

- 2 Software Start up

-

3 User Interface

- 3.1

Toolbar

- 3.1.1 File Options

- 3.1.2 Instrument Options

- 3.1.3 Data Capture Option

- 3.1.4

Test Options

- 3.1.4.1 Notch Frequency Bins

- 3.1.4.2 2 Channel Display and Cursor Lock

- 3.1.4.3 Analysis Window Markers

- 3.1.4.4 X-Scale in Time

- 3.1.4.5 Y-Scale in Voltage

- 3.1.4.6 Other Frequency Options

- 3.1.4.7 NSD Marker

- 3.1.4.8 Phase Plot

- 3.1.4.9 Phase in Degree

- 3.1.4.10 Histogram

- 3.1.4.11 Disable User Popups

- 3.1.4.12 HSDC Pro Lite Version

- 3.1.5 Help

- 3.2 Status Windows

- 3.3 Mode Selection

- 3.4 Device Selection

- 3.5 Skip Configuration

- 3.6 Capture Button (ADC Mode Only)

- 3.7 Test Selection (ADC Mode only)

- 3.8 DAC Display Panel (DAC Mode only)

- 3.9 I/Q Multi-Tone Generator

- 3.1

Toolbar

- 4 ADC Data Capture Software Operation

- 5 TSW1400 Pattern Generator Operation

- 6 TSW14J58 Functional Description

- 7 TSW14J57 Functional Description

- 8 TSW14J56 Functional Description

- 9 TSW14J50 Functional Description

- 10TSW14J10 Functional Description

- A Signal Processing in High Speed Data Converter Pro

- B History Notes

- C Revision History

3.1.2.2 IO Delay

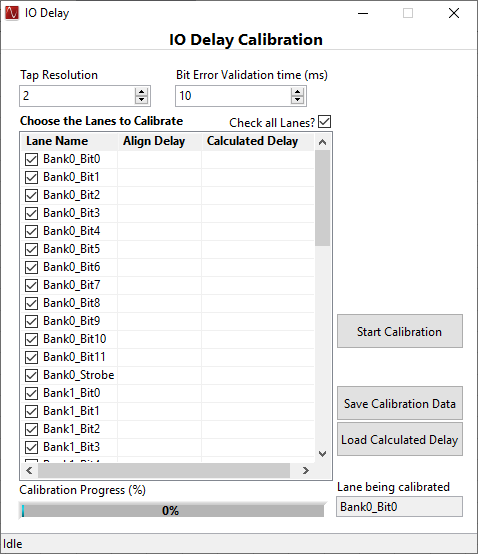

The “IO Delay” Calibration process sweeps the IO Delay tap values across a lane and get the tap values where there are no bit errors. Selecting the IO Delay opens the window shown in Figure 3-6. This allows the user to calibrate the lane wise delay adjustments.

Figure 3-6 IO Delay Calibration

Figure 3-6 IO Delay CalibrationCalibration is done sequentially for the selected lanes, one after the other. The “Tap Resolution” denotes the minimum step size with which the tap values are swept across IO Delay tap values. “Bit Error Validation time (ms)” specifies the time delay to wait before checking if the Error Bit is true/false while sweeping across the IO Delay tap vales. “Check all Lanes?” can be used to check/uncheck all the lanes. After selecting the required lanes to calibrate, click on the “Start Calibration Data” button to run the calibration on the selected lanes one after the other. Once calibration has been started (“Start Calibration” then turns into “Stop Calibration”), it can be stopped anytime using “Stop Calibration” button. After the calibration completes, the calibrated data can be saved by clicking on “Save Calibration Data” and entering the target file location. Click on “Load Calculated Delay” and load the previously saved file with Calibration data, this action derives the “Calculated Delay” for all the selected/calibrated lanes and the same calculated delay gets loaded to the FW. This completes the IO Delay Calibration. After the IO Delay Calibration steps are done, data capture can be done from HSDC Pro as usual.