SLWU087E november 2013 – june 2023

- 1

- High Speed Data Converter Pro GUI

- Trademarks

- 1 Introduction

- 2 Software Start up

-

3 User Interface

- 3.1

Toolbar

- 3.1.1 File Options

- 3.1.2 Instrument Options

- 3.1.3 Data Capture Option

- 3.1.4

Test Options

- 3.1.4.1 Notch Frequency Bins

- 3.1.4.2 2 Channel Display and Cursor Lock

- 3.1.4.3 Analysis Window Markers

- 3.1.4.4 X-Scale in Time

- 3.1.4.5 Y-Scale in Voltage

- 3.1.4.6 Other Frequency Options

- 3.1.4.7 NSD Marker

- 3.1.4.8 Phase Plot

- 3.1.4.9 Phase in Degree

- 3.1.4.10 Histogram

- 3.1.4.11 Disable User Popups

- 3.1.4.12 HSDC Pro Lite Version

- 3.1.5 Help

- 3.2 Status Windows

- 3.3 Mode Selection

- 3.4 Device Selection

- 3.5 Skip Configuration

- 3.6 Capture Button (ADC Mode Only)

- 3.7 Test Selection (ADC Mode only)

- 3.8 DAC Display Panel (DAC Mode only)

- 3.9 I/Q Multi-Tone Generator

- 3.1

Toolbar

- 4 ADC Data Capture Software Operation

- 5 TSW1400 Pattern Generator Operation

- 6 TSW14J58 Functional Description

- 7 TSW14J57 Functional Description

- 8 TSW14J56 Functional Description

- 9 TSW14J50 Functional Description

- 10TSW14J10 Functional Description

- A Signal Processing in High Speed Data Converter Pro

- B History Notes

- C Revision History

10.2 DAC38J84EVM GUI Setup Example

The following example shows what must be modified in the DAC3XJ8X GUI for a setup using 4 lanes, 1x interpolation, and a DAC sample rate of 368.64M.

After opening the DAC GUI, enter the parameters as shown in Figure 10-2.

Figure 10-2 Quick

Start Menu

Figure 10-2 Quick

Start MenuThe GUI calculates the lane rate and displays it in the box called SerDes Linerate. For this example, the lane rate is 7372.8Mbps. Using the lane rate conditions in Section 10.1, REFCLK = 368.64 MHz and Core clock = 184.32 MHz.

Click on the Program LMK04828 and DAC3XJ8X button. After the programming has completed, click on the LMK04828 Controls tab. Next click on the Clock Outputs tab.

For the DAC3XJ8X GUI, the REFCLK is provided by CLKout 0 and the Core clock is provided by CLKout 12. Notice that the default setting for CLKout 12 is Group Powerdown, as shown in Figure 10-3.

Figure 10-3 LMK04828 Clock Outputs Menu

Figure 10-3 LMK04828 Clock Outputs MenuSince the DAC Clock is 368.64 MHz, to provide a REFCLK of 368.64 MHz, change the DCLK Divider for CLKout 0 to “8”.

To generate a Core clock of 184.32 MHz, set the DCLK Divider for CLKout 12 to “16”. Also, remove the checkmark from the Group Powerdown box to enable this output. The Clock Outputs menu is now as seen in Figure 10-4.

Figure 10-4 LMK04828 Clock Outputs Menu

Figure 10-4 LMK04828 Clock Outputs MenuOpen HSDC Pro GUI, select the DAC tab, then select DAC3XJ84_LMF_442 in the device button. After the firmware is loaded, enter 368.64M in the Data Rate (SPS) window, select 2’s Complement in the DAC Option window and generate a 10-MHz test tone using the IQ Multitone Generator located in the lower left of the GUI. Click on the Create Tones button. The display looks as shown in Figure 10-5.

Figure 10-5 HSDC Pro GUI

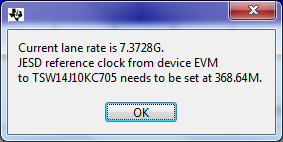

Figure 10-5 HSDC Pro GUIClick the Send button. A new window opens showing the lane rate of the interface and the required frequency of REFCLK, as shown in Figure 10-6.

Figure 10-6 HSDC Pro GUI: Lane Rate and REFCLK Settings

Figure 10-6 HSDC Pro GUI: Lane Rate and REFCLK SettingsGo back to the DAC GUI Quick Start tab and click on Reset DAC JESD Core. Click on Trigger LMK04828 SYSREF. There should now be a 10-MHz tone present at all four DAC EVM outputs.