JAJSM94B June 2021 – June 2022 DAC12DL3200

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics - DC Specifications

- 6.6 Electrical Characteristics - Power Consumption

- 6.7 Electrical Characteristics - AC Specifications

- 6.8 Timing Requirements

- 6.9 Switching Characteristics

- 6.10 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 DAC Output Modes

- 7.3.2 DAC Output Interface

- 7.3.3 LVDS Interface

- 7.3.4 Multi-Device Synchronization (SYSREF+/-)

- 7.3.5 Alarms

- 7.4 Device Functional Modes

- 7.5 Programming

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

8.2 Typical Application

The DAC12DL3200 can be used in a wide range of applications including radar, electronic warfare, satellite communications, test equipment (communications testers and arbitrary waveform generators) and software-defined radios (SDRs).

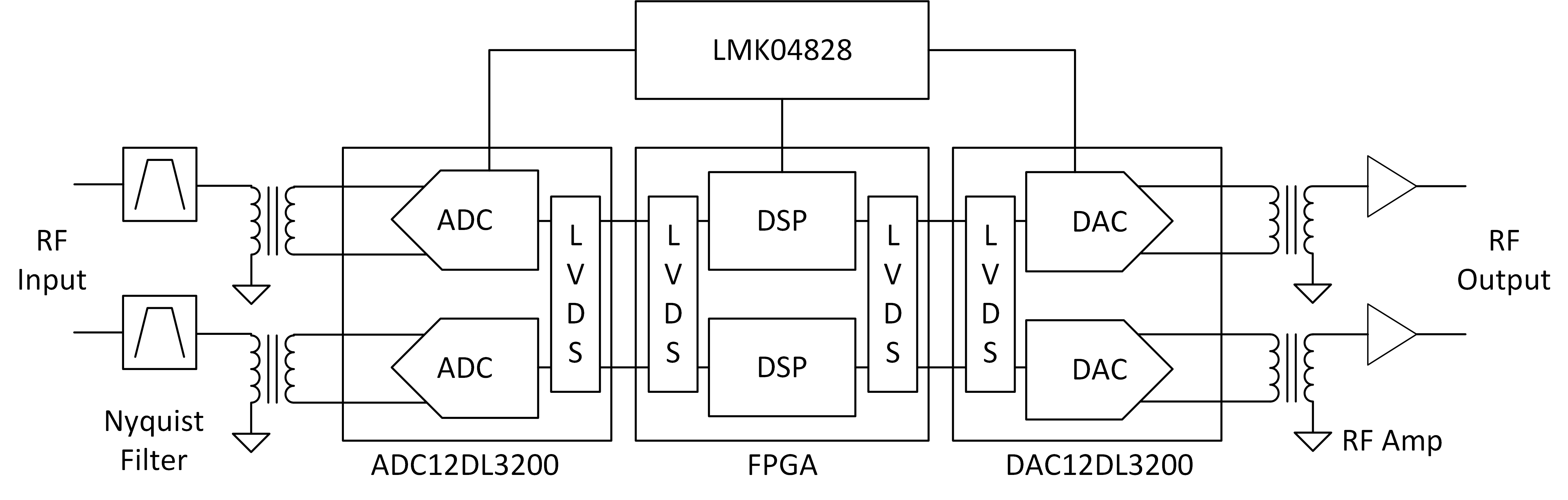

The low latency of the DAC12DL3200, in combination with the low latency ADC12DL3200, make it particularly suitable for electronic warfare applications where a fast return of the pulse is important to as closely match the reflected pulse in time. Figure 8-1 shows a block diagram for an electronic warfare digital radio. The received radio pulse (after amplification) is input to the ADC12DL3200, the digital signal transferred to the FPGA for digital signal processing (for example frequency or delay shifting), and output by the DAC12DL3200 at the same frequency as the input to the ADC. The DAC and ADC are clocked by the LMK04828.

Figure 8-1 System Block Diagram for a Electronics Warfare Digital Radio

Figure 8-1 System Block Diagram for a Electronics Warfare Digital Radio