SPRACN0F October 2021 – March 2023 F29H850TU , F29H859TU-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- The Essential Guide for Developing With C2000™ Real-Time Microcontrollers

- Trademarks

- 1C2000 and Real-Time Control

-

2Sensing Key Technologies

- 2.1 Accurate Digital Domain Representation of Analog Signals

- 2.2 Optimizing Acquisition Time vs Circuit Complexity for Analog Inputs

- 2.3 Hardware Based Monitoring of Dual-Thresholds Using a Single Pin Reference

- 2.4 Resolving Tolerance and Aging Effects During ADC Sampling

- 2.5 Realizing Rotary Sensing Solutions Using C2000 Configurable Logic Block

- 2.6 Smart Sensing Across An Isolation Boundary

- 2.7 Enabling Intra-Period Updates in High Bandwidth Control Topologies

- 2.8 Accurate Monitoring of Real-Time Control System Events Without the Need for Signal Conditioning

-

3Processing Key Technologies

- 3.1 Accelerated Trigonometric Math Functions

- 3.2 Fast Onboard Integer Division

- 3.3 Hardware Support for Double-Precision Floating-Point Operations

- 3.4 Increasing Control Loop Bandwidth With An Independent Processing Unit

- 3.5 Flexible System Interconnect: C2000 X-Bar

- 3.6 Improving Control Performance With Nonlinear PID Control

- 3.7 Understanding Flash Memory Performance In Real-Time Control Applications

- 3.8 Deterministic Program Execution With the C28x DSP Core

- 3.9 Efficient Live Firmware Updates (LFU) and Firmware Over-The-Air (FOTA) updates

-

4Control Key Technologies

- 4.1 Reducing Limit Cycling in Control Systems With C2000 HRPWMs

- 4.2 Shoot Through Prevention for Current Control Topologies With Configurable Deadband

- 4.3 On-Chip Hardware Customization Using the C2000 Configurable Logic Block

- 4.4 Fast Detection of Over and Under Currents and Voltages

- 4.5 Improving System Power Density With High Resolution Phase Control

- 4.6 Safe and Optimized PWM Updates in High-Frequency, Multi-Phase and Variable Frequency Topologies

- 4.7 Solving Event Synchronization Across Multiple Controllers in Decentralized Control Systems

- 5Interface Key Technologies

- 6Safety Key Technologies

- 7References

- 8Revision History

2.7.2 In Depth

While choosing a discrete ADC for a system many factors are considered: raw converter speed, DC error terms like gain and offset, and AC error terms like SNR, THD(Shown in:GUID-11864FD1-B99D-4993-B4BE-E4A724B34373.html#GUID-11864FD1-B99D-4993-B4BE-E4A724B34373). Beyond those parameters are the aspects of system integration, conversion speed with respect to the control loop, and sampling capability that can make or break a real-time control design.

System integration: One advantage of an integrated ADC is the lack of an external communications bus that adds complexity to the system in both latency of the comms channel but also noise considerations for bus routing. Once the ADC conversion is complete, minimizing the delay into the control scheme of the system is vital. The ADC results are accessible by all CPU cores, CLA cores, as well as DMAs.

Another common delay is introduced due to the latency introduced when the CPU is notified that the ADC conversion is complete. The C2000 ADCs implement a selectable early interrupt that takes advantage of the time the ADC incurs between the start of a sample and the completion of the analog to digital conversion. Since the ADC is integrated the C2000 MCU has the ability to sychronize to either the end of the analog sampling phase or the full conversion complete. This allows the C28x CPU or CLA to continue to do other tasks or calculations in parallel to the ADC conversion and use the ADC conversion as soon as it is available. Not only are wasted cylces minimized, but results in a more stable system control as the converted value used by the CPU is closer in time to the real world signal state.

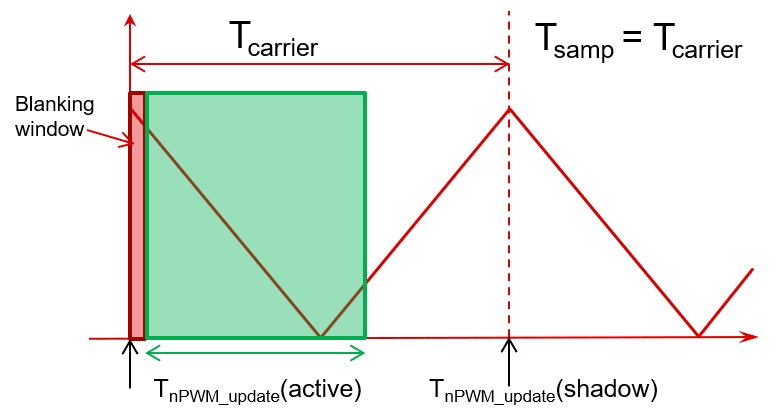

Conversion Speed:One aspect that is common in the evaluation of any ADC, discrete or integrated, is its conversion speed. This is how long it takes the ADC to convert the sampled analog signal into a digital representation. This is especially important in high bandwidth systems as it is beneficial to update the system intracycle vs waiting for the next full cycle of the control loop to happen (#GUID-2F5538C9-34DF-485C-9C58-C9CFED25ABB2). This is shown the (Fast Current Loop examples). The ADC on the C2000 MCU is capable of generating a conversion in as little as 260ns after the sample completes. This allows enough time for the C28x or CLA core to calculate the new PWM frequencies well ahead of the next control loop period allowing for the intra-cycle update to happen. The ePWM module plays a role here as well, allowing the PWM to be updated by writing to the active registers vs the shadow resigster, which would pend the update until the next full period.

Figure 2-10 Intra-Period Update of PWM

Figure 2-10 Intra-Period Update of PWM Simultaneous sampling: Each C2000 device referenced in this guide has at least 2 if not more ADCs. Looking at common real-time control topologies this allows simultaneous sampling of the motor currents. For the case of a system that uses a resolver for posistion sensing this would allow both the sine and cosine feedbacks to be sampled at the same point in time. Table 2-4 shows the potential effect on the system if such inputs are not sampled at the same point in time

| Control Loop Frequency | Phase Error With 500ns Sample Lag | Phase Error With 1µs Sample Lag |

|---|---|---|

| 10 kHz | 1.8 degrees | 3.6 degrees |

| 20 kHz | 3.6 degrees | 7.2 degrees |

| 50 kHz | 8.9 degrees | 17.8 degrees |