SPRACT6A october 2020 – march 2023 F29H850TU , F29H850TU , F29H859TU-Q1 , F29H859TU-Q1 , TMS320F2800132 , TMS320F2800132 , TMS320F2800133 , TMS320F2800133 , TMS320F2800135 , TMS320F2800135 , TMS320F2800137 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280023C , TMS320F280025 , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280033 , TMS320F280034 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C , TMS320F280049C-Q1 , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28076 , TMS320F28374D , TMS320F28374D , TMS320F28374S , TMS320F28374S , TMS320F28375D , TMS320F28375D , TMS320F28375S , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376D , TMS320F28376S , TMS320F28376S , TMS320F28377D , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378D , TMS320F28378S , TMS320F28378S , TMS320F28379D , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28379S , TMS320F28384D , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388D , TMS320F28388S , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1 , TMS320F28P659SH-Q1

- Abstract

- Trademarks

- 1Introduction

- 2Input Settling Design Steps

-

3Example Circuit Design

- 3.1 Select the ADC

- 3.2 Find the Minimum Op-Amp Bandwidth and RC Filter Ranges

- 3.3 Verify the Op-amp Model

- 3.4 Build the ADC Input Model

- 3.5 DC Node Analysis

- 3.6 Refine RC Filter Values Via Simulation (Part 1)

- 3.7 Refine RC Filter Values Via Simulation (Part 2)

- 3.8 Refine RC Filter Values Via Simulation (Part 3)

- 3.9 Further Refinement

- 3.10 Further Simulations

- 3.11 Completed Worksheet

- 4Working With Existing Circuits or Additional Constraints

- 5Summary

- 6References

- 7Revision History

3.7 Refine RC Filter Values Via Simulation (Part 2)

Now that the basic simulation has shown that the simulation is fundamentally working, sweeps can be performed to refine the Rs component selection.

To perform a sweep, click on the sweep button, then click on the Vcont voltage source (which controls the value of Rs).

Figure 3-7 Sweep Button

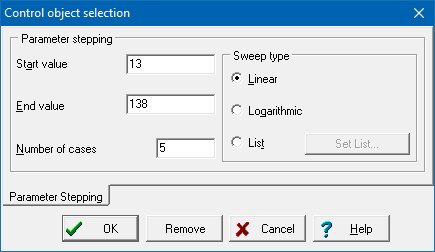

Figure 3-7 Sweep ButtonThis will bring up a dialog box. Select the "..." button next to the Voltage [V] parameter and configure the sweep to select 5 points on a linear scale from 13 Ω to 138 Ω as shown in Figure 3-8.

Figure 3-8 F280049 Example Sweep Control

Dialog

Figure 3-8 F280049 Example Sweep Control

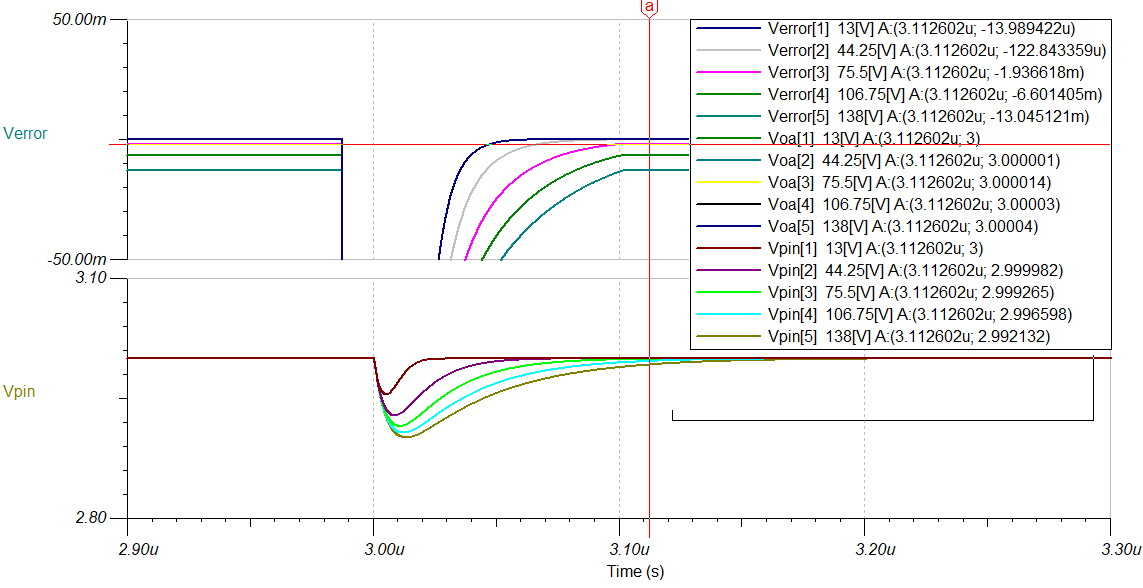

DialogThe output of the transient simulation with a sweep of Rs is shown in Figure 3-9. Note that the outputs have again been separated, and all outputs other than Vpin and Verror have been deleted. Verror range has been set to -50 mV to +50 mV and the waveform has been limited to better observe the settling.

From this output, it can be concluded:

- Higher resistance values in the Rs range do not provide quick enough settling. For instance, 106 Ω only settles to 6.6 mV in the allocated S+H time while the settling target is 366 µV

- A good range for further investigation would be 10 Ω to 50 Ω

Figure 3-9 F280049 Example Rs

Initial Sweep Results

Figure 3-9 F280049 Example Rs

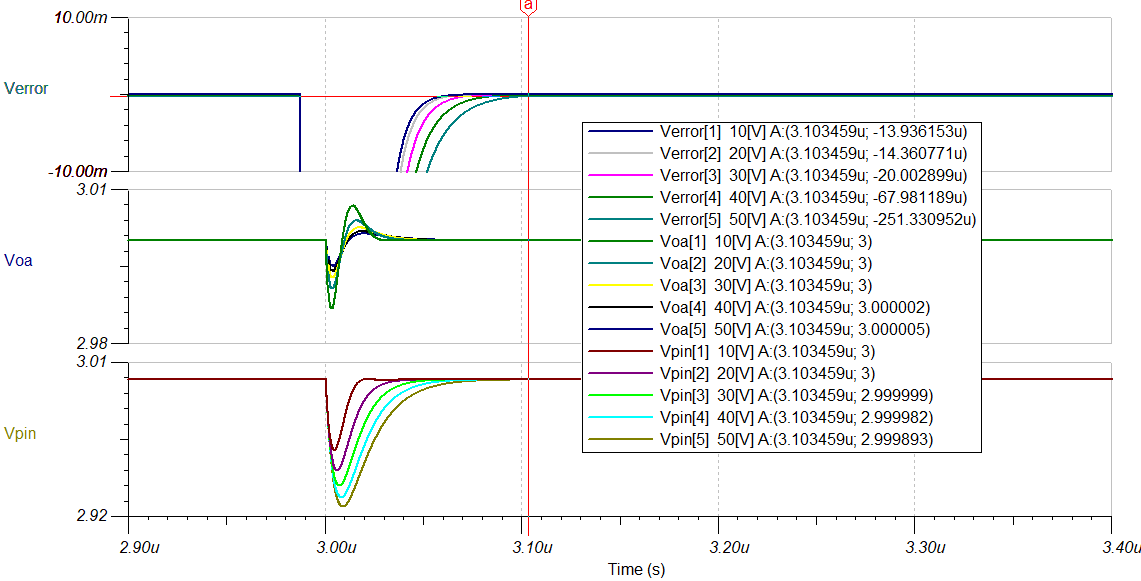

Initial Sweep ResultsFigure 3-10 shows the results of a sweep of Rs from 10 Ω to 50 Ω. From this set of waveforms, it appears that values of Rs from 10 Ω to 30 Ω all provide settling that greatly exceeds the design target. A final value of Rs was thus selected as 27 Ω.

Figure 3-10 F280049 Example Rs

Fine Sweep Results

Figure 3-10 F280049 Example Rs

Fine Sweep Results