TIDUD61E October 2020 – April 2021

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements, and Test Results

- 3.1

Required Hardware and Software

- 3.1.1 Hardware

- 3.1.2

Software

- 3.1.2.1 Opening Project Inside CCS

- 3.1.2.2 Project Structure

- 3.1.2.3 Using CLA on C2000 MCU to Alleviate CPU Burden

- 3.1.2.4 CPU and CLA Utilization and Memory Allocation

- 3.1.2.5

Running the Project

- 3.1.2.5.1 Lab 1: Open Loop, DC (PFC Mode)

- 3.1.2.5.2 Lab 2: Closed Current Loop DC (PFC)

- 3.1.2.5.3 Lab 3: Closed Current Loop, AC (PFC)

- 3.1.2.5.4 Lab 4: Closed Voltage and Current Loop (PFC)

- 3.1.2.5.5 Lab 5: Open loop, DC (Inverter)

- 3.1.2.5.6 Lab 6: Open loop, AC (Inverter)

- 3.1.2.5.7 Lab 7: Closed Current Loop, DC (Inverter with resistive load)

- 3.1.2.5.8 Lab 8: Closed Current Loop, AC (Inverter with resistive load)

- 3.1.2.5.9 Lab 9: Closed Current Loop (Grid Connected Inverter)

- 3.1.2.6 Running Code on CLA

- 3.1.2.7

Advanced Options

- 3.1.2.7.1 Input Cap Compensation for PF Improvement Under Light Load

- 3.1.2.7.2 83

- 3.1.2.7.3 Adaptive Dead Time for Efficiency Improvements

- 3.1.2.7.4 Phase Shedding for Efficiency Improvements

- 3.1.2.7.5 Non-Linear Voltage Loop for Transient Reduction

- 3.1.2.7.6 Software Phase Locked Loop Methods: SOGI - FLL

- 3.2 Testing and Results

- 3.1

Required Hardware and Software

- 4Design Files

- 5Software Files

- 6Related Documentation

- 7About the Author

- 8Revision History

3.1.2.5.4.2 Designing Voltage Loop Compensator

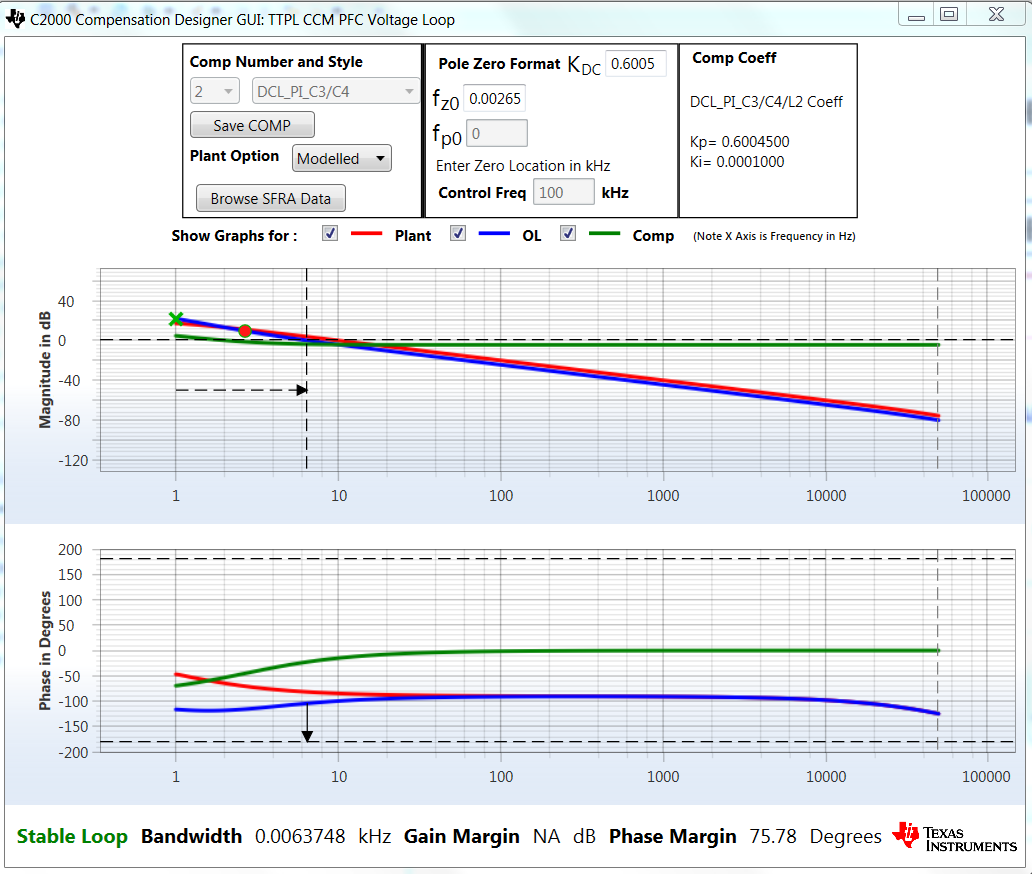

- Compensation designer then launches with the model of the voltage loop plant, as shown in Figure 3-26. The PI compensator can be edited to get the desired gain and phase margin, keeping in mind the bandwidth of the voltage loop has an inverse relationship with the THD achieved. Typically in a PFC application, this bandwidth is kept at approximately 10 Hz.

Figure 3-26 Voltage Loop PI Compensation Tuning Using Compensation Designer

Figure 3-26 Voltage Loop PI Compensation Tuning Using Compensation Designer - Once satisfied with the compensator design, click on Save COMP. This action saves the compensator values into the project.

- Note: If the project was not selected from the solution adapter, changes to the compensator are not allowed. To design one's own, select the solution through the solution adapter.

- Close the Compensation Designer, and return to the powerSUITE page. Save using Ctrl + S.