SPRAC21A June 2016 – June 2019 OMAP-L132 , OMAP-L138 , TDA2E , TDA2EG-17 , TDA2HF , TDA2HG , TDA2HV , TDA2LF , TDA2P-ABZ , TDA2P-ACD , TDA2SA , TDA2SG , TDA2SX , TDA3LA , TDA3LX , TDA3MA , TDA3MD , TDA3MV

-

TDA2xx and TDA2ex Performance

- Trademarks

- 1 SoC Overview

- 2 Cortex-A15

- 3 System Enhanced Direct Memory Access (System EDMA)

- 4 DSP Subsystem EDMA

- 5 Embedded Vision Engine (EVE) Subsystem EDMA

- 6 DSP CPU

- 7 Cortex-M4 (IPU)

- 8 USB IP

- 9 PCIe IP

- 10 IVA-HD IP

- 11 MMC IP

- 12 SATA IP

- 13 GMAC IP

- 14 GPMC IP

- 15 QSPI IP

- 16 Standard Benchmarks

- 17

Error Checking and Correction (ECC)

- 17.1 OCMC ECC Programming

- 17.2 EMIF ECC Programming

- 17.3 EMIF ECC Programming to Starterware Code Mapping

- 17.4 Careabouts of Using EMIF ECC

- 17.5 Impact of ECC on Performance

- 18 DDR3 Interleaved vs Non-Interleaved

- 19 DDR3 vs DDR2 Performance

- 20 Boot Time Profile

- 21 L3 Statistics Collector Programming Model

- 22 Reference

- Revision History

10.1 Overview

HDVICP2/IVAHD is TIs second generation Video and Imaging co-processor designed to accelerate the HD Video encoding and decoding. It is a successor to the HDVICP 1.0. Both generations support 4:2:0 Chroma formats only. HDVICP2 is sometimes referred to as IVAHD 1.0. The DM46x devices are some of the SoCs that have HDVICP 1.0.

DM816x, DM814x, DM813x, OMAP4, and OMAP5 are some of the SoCs that have HDVICP 2.0. These different SoCs have varying number of instances of HDVICP2 and operating frequency. For more details, see the device-specific data sheet.

The block diagram of IVAHD is shown in Figure 30.

Figure 30. IVAHD Block Diagram

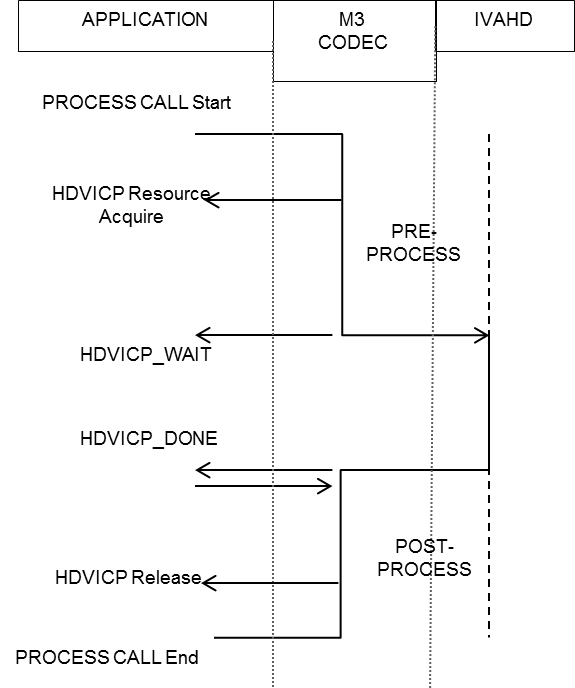

Figure 30. IVAHD Block Diagram The typical process call structure for the IVAHD codecs that encodes or decodes a single frame of a single channel of encode or decode is shown in Figure 31. The major performance probe points are:

- Process Call Start – Begin the CODEC operation.

- HDVICP2 Resource Acquire – Acquire IVAHD resource to start IVAHD operations.

- HDVICP2 Wait – M4 pre-processing completes. M4 can perform a thread switch to perform some other operation while IVAHD performs encode or decode operations.

- HDVICP2 Done – M4 receives a completion interrupt from IVAHD and switches back to the codec thread.

- HDVICP2 Release – M4 post processing thread releases the IVAHD resource.

- Process Call End – Completion of the frame encodes or decode operation.

Figure 31. IVAHD Software Performance Probe Points

Figure 31. IVAHD Software Performance Probe Points