SPRAD62 February 2023 F29H850TU , F29H859TU-Q1 , TMS320F280023C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038C-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- Abstract

- Trademarks

- 1Introduction

- 2Serial Port Design Methodology

- 3Example A: Using the CLB to Input and Output a TDM Stream in Audio Applications

- 4Example B: Using the CLB to Implement a Custom Communication Bus for LED Driver in Lighting Applications

- 5References

2.5 Step 5: Simulate the Logic Design

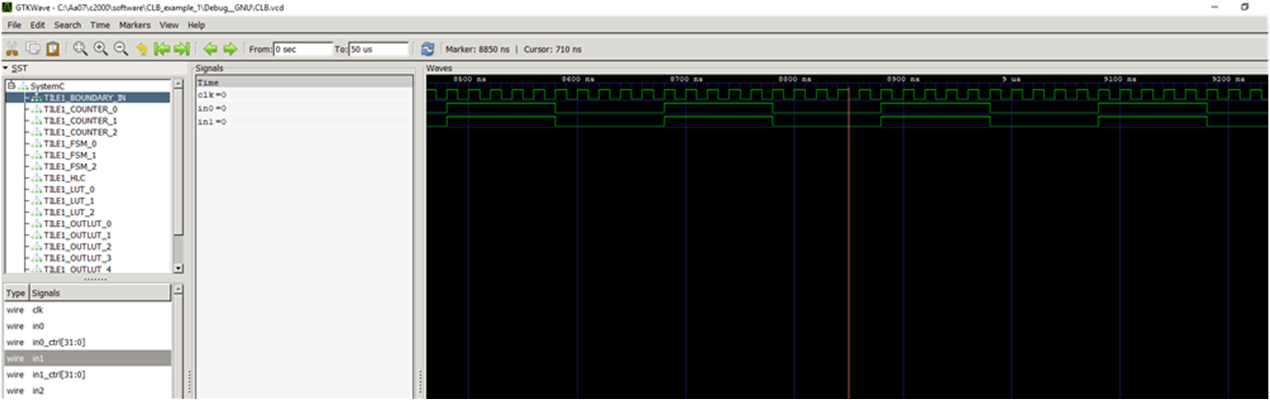

A serial interface design can quickly become very complex due to the different logic blocks and interconnections used in the design. In order to facilitate debugging of the CLB logic design, the CLB tool generates an interconnect block diagram (Figure 2-5) and a simulation waveform (Figure 2-6). For more details on how to generate these two files, see the CLB Tool User’s Guide.

Figure 2-6 CLB Simulation Example

Figure 2-6 CLB Simulation Example