SPRUIW7A October 2020 – February 2022

- Trademarks

- 1Introduction

- 2J7200 EVM Overview

- 3EVM User Setup/Configuration

-

4J7200 EVM Hardware Architecture

- 4.1 J7200 EVM Hardware Top Level Diagram

- 4.2 J7200 EVM Interface Mapping

- 4.3 I2C Address Mapping

- 4.4 GPIO Mapping

- 4.5 Power Supply

- 4.6 Reset

- 4.7 Clock

- 4.8 Memory Interfaces

- 4.9 MCU Ethernet Interface

- 4.10 QSGMII Ethernet Interface

- 4.11 PCIe Interface

- 4.12 USB Interface

- 4.13 Audio Interface

- 4.14 CAN Interface

- 4.15 FPD Interface (Audio Deserializer)

- 4.16 I3C Interface

- 4.17 ADC Interface

- 4.18 RTC Interface

- 4.19 Apple Authentication Header

- 4.20 JTAG Emulation

- 4.21 EVM Expansion Connectors

- 4.22 ENET Expansion Connector

- 5Functional Safety

- 6Revision History

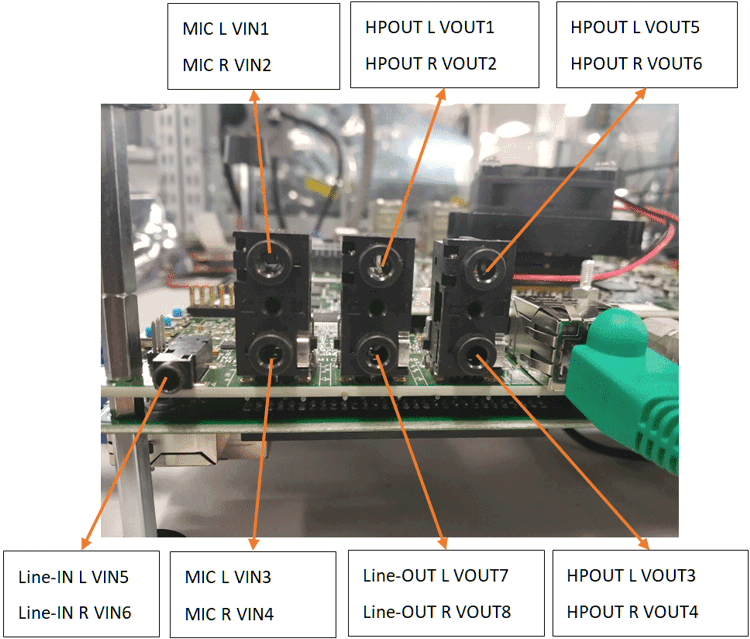

4.13.5 Port Mapping

Common Processor board audio ports are mapped as below.

- 3x Standard 3.5mm stacked Stereo

Audio Jack Mfr. Part# STX-4235-3/3-N is provided for:

- 2x – MIC IN, 1x – Line OUT and 3x – Head Phone OUT.

- 1x Standard 3.5mm Stereo Audio Jack

Mfr. Part# SJ-3524-SMT-TR provided for:

- 1x – Line IN interface.

Figure 4-29 Audio Port Interface

Assignment

Figure 4-29 Audio Port Interface

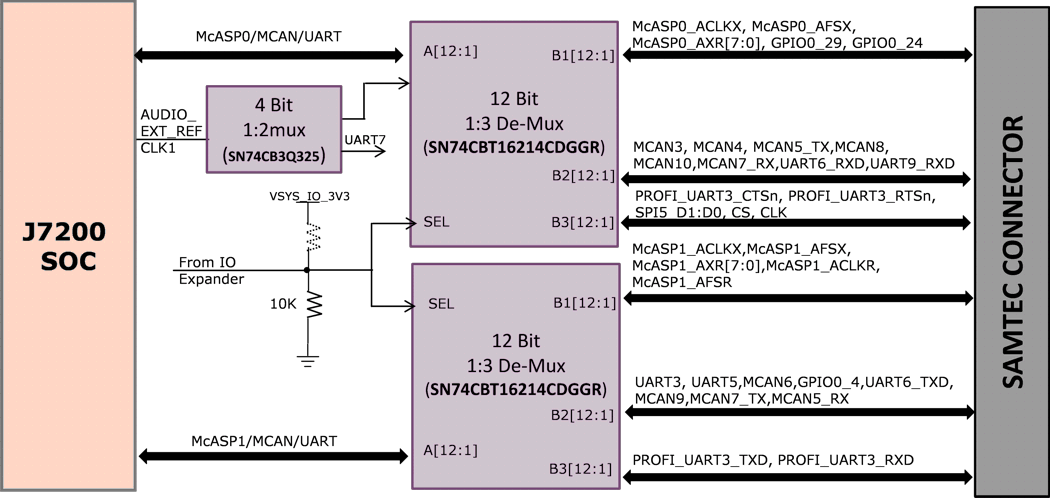

AssignmentMcASP0 and McASP1 of J7200 SoC is muxed with UART and MCAN interface. J7200 SOM includes two 1:3 De-Mux (Mfr. Part# SN74CBTLV16292GR) to support Audio codec and Trace functions on the CP Board and MCAN/LIN on the J7x GESI Expansion board. Default channel selection will be done for McASP/TRACE interface through Resistor strap and GPIO from GPIO expander on the J7200 SoC will change the configuration.

AUDIO_EXT_REF_CLK1 of J7200 SoC is used for System Reference clock input of the Audio codec. 4bit 1:2 mux IC is used to route the clock input to the McASP/MCAN mux as shown in Figure 4-30.

Figure 4-30 McASP/TRACE/MCAN Mux

Circuit

Figure 4-30 McASP/TRACE/MCAN Mux

Circuit| MUX_SEL2 | MUX_SEL1 | MUX_SEL0 | FUNCTION |

|---|---|---|---|

| HIGH | HIGH | LOW | A port0 = B1 port |

| HIGH | HIGH | HIGH | A port0 = B2 port (default) |

| HIGH | LOW | HIGH | A port0 = B3 port |

Port B1: McASP0/1 and TRACE

Port B2: MCAN/UART

Port B3: PROFI_UART/SPI