SSZTC63 September 2015 AM3357 , AM3359 , DP83822H , DP83825I , DP83826E , DP83826I , DP83848-HT , DP83848C , DP83848H , DP83848I , DP83848J , DP83848K , DP83848M , DP83848T , DP83848VYB , DP83848YB , DP83867CR , DP83867CS , DP83867E , DP83867IR , DP83867IS

Welcome back to the second installment of “How to select the right industrial Ethernet standard,” a blog series for designers who have decided to leverage industrial Ethernet in their systems. This series will cover several common industrial Ethernet communication protocols to help you select the best standard for your application. You can read the previous post, about Sercos III, here.

In this installment, I’ll take a close look at EtherCAT, its end applications and how it works.

Beckhoff Automation invented EtherCAT. Since 2003, it has been under the umbrella of the EtherCAT Technology Group (ETG), an industrial fieldbus organization with around 2,600 member companies.

EtherCAT can be found in factory automation, semiconductor tools, packaging robotics and more. One of my favorite nonindustrial examples is the World of Color show in Disneyland, where EtherCAT controls the light show.

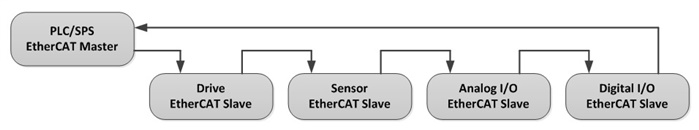

On the technical side, EtherCAT is a master-and-slave network architecture as shown in Figure 1. The EtherCAT slave has two Ethernet connectors in order to support a simple line topology. It is also possible to support a ring topology for redundancy, in which case the EtherCAT master also needs two Ethernet ports. An EtherCAT network can support up to 65,535 slave devices.

Figure 1 EtherCAT Master-and-slave

Example Network with EtherCAT Frame Flow

Figure 1 EtherCAT Master-and-slave

Example Network with EtherCAT Frame FlowOnly the EtherCAT master generates an EtherCAT frame; all slaves receive and process this frame. The last slave loops back the EtherCAT frame, and it travels back through all slaves (without further processing) to the master. The EtherCAT frame has reserved space for process data for each slave, and none of the slaves change the frame length itself. It is a bit like a train with multiple cars and seats for passengers, where each slave has an assigned car or an assigned seat. EtherCAT allows addressing down to the “seat” level – the bit level in process data.

An EtherCAT master requires a standard Ethernet MAC peripheral only as the master has no specific need to process the EtherCAT frame in real-time.The master only needs to trigger the start of an EtherCAT frame with an accurate time base.

An EtherCAT slave requires specific Ethernet hardware (EtherCAT MAC) support – typical implementations use Application Specific Integrated Circuits (ASIC) or Field Programmable Gate Arrays (FPGA) as seen in Figure 2 – as it needs to process incoming EtherCAT frames on the fly. This means that EtherCAT MAC processes the EtherCAT frame while frame reception is ongoing. Typical EtherCAT devices have a 1µs port-to-port delay between received and transmitted frames.

Figure 2 EtherCAT Slave with an

ASIC/FPGA and External Processor

Figure 2 EtherCAT Slave with an

ASIC/FPGA and External ProcessorThe EtherCAT standard does not allow other types of Ethernet frames in an EtherCAT network. This is mainly to keep the real-time Ethernet channel clear for EtherCAT frames. In case a non-EtherCAT frame (an EtherType not matching with EtherCAT) is in the EtherCAT network, the EtherCAT slaves will destroy the frame by invalidating the frame checksum (CRC). This makes the none-EtherCAT frame useless for standard Ethernet devices, and they will sooner or later stop “polluting” the EtherCAT network.

It is possible to transmit standard Ethernet frames (Transmission Control Protocol/Internet Protocol (TCP/IP), User Datagram Protocol (UDP)) over an EtherCAT network by encapsulating the Ethernet frame into an EtherCAT frame. This is done through various EtherCAT profiles that sit on top of the EtherCAT host-processor stack. An example profile is the Ethernet over EtherCAT profile.

Other features and functions of EtherCAT devices include:

- Distributed clocks – a precise time-synchronization method across the slaves and the master.

- Fast link-drop detection with loopback (requiring Ethernet PHY transceiver support) – when the Ethernet PHY, such as the DP83826E, detects a link down, it notifies the EtherCAT hardware. Within less than 10µs, the EtherCAT hardware will loop back the EtherCAT frames.

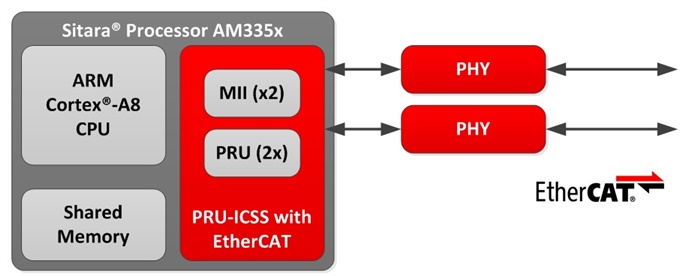

Using an ASIC or FPGA for EtherCAT adds cost and board space. An alternative solution is to use the PRU-ICSS peripheral in many TI Sitara processors. For example, TI provides PRU-ICSS firmware for the AM335x processor, enabling an EtherCAT slave device without the use of an external FPGA (Figure 3). You can evaluate TI’s EtherCAT slave solution with the TMDSICE3359 evaluation board.

Figure 3 EtherCAT Slave Integrated with

a TI Sitara Processor

Figure 3 EtherCAT Slave Integrated with

a TI Sitara ProcessorI hope this post has shed some light into EtherCAT’s functionality. Make sure to read additional posts in this series to learn more about the many industrial Ethernet standards.

Additional Resources

- View the EtherCAT Slave and Multi-Protocol Industrial Ethernet Reference Design

- Read the previous post in this series, “How to select the right industrial Ethernet standard: Sercos III.”

- Read a blog post on “How to make industrial Ethernet as simple as a standard Ethernet.”

- Read the white paper, “EtherCAT on Sitara Processors,” which provides an introduction to EtherCAT.

- Take an inside look at industrial Ethernet communication protocols in this white paper.

- Learn more about the EtherCAT standard on the ETG website.