JAJU510H March 2018 – December 2022

- 概要

- リソース

- 特長

- アプリケーション

- 5

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements, and Test Results

- 3.1 Required Hardware and Software

- 3.2 Testing and Results

- 4Design Files

- 5Trademarks

- 6About the Authors

- 7Revision History

3.2.2.3 Lab 4

In this lab the power stage is run in a closed loop with grid connection on HIL platform. Figure 3-14 shows the SW diagram.

Set the project to Lab 4 by changing the Lab Number in the <settings.h> file, (this will be changed by powerSUITE GUI when using powerSUITE project).

In the user settings.h file some additional options are available, but the following are used for the tests documented in this user guide.

#if TINV_LAB == 4

#define TINV_TEST_SETUP TINV_TEST_SETUP_GRID_CONNECTED

#define TINV_PROTECTION TINV_PROTECTION_ENABLED

#define TINV_SFRA_TYPE TINV_SFRA_CURRENT

#define TINV_SFRA_AMPLITUDE (float32_t)TINV_SFRA_INJECTION_AMPLITUDE_LEVEL2

#define TINV_POWERFLOW_MODE TINV_INVERTER_MODE

#define TINV_DC_CHECK 0

#define TINV_SPLL_TYPE TINV_SPLL_SRF

#endifLab 4

In this check, the SW is run on the HIL platform.

Build and load the code, use the lab4.js file to populate the watch variables in the CCS window.

- Slowly ramp the DC bus voltage 'Vbus' to 800 V

- Enter "1" on TINV_startPowerStage variable and ramp the AC voltage of the grid to 230Vrms, L-N; that is, 400 VL-L

- Set up an appropriate grid connection and turn on the relay by writing a 1 to TINV_allRelaySet as soon as voltage reaches 230 VRMS as the inrush current limit resistors might get heated and burn out. The current should now be fed into the grid.

- Slowly increase this TINV_idRef_pu variable to be 0.6 pu, at this point the per phase power will be approximately 1.9 kW

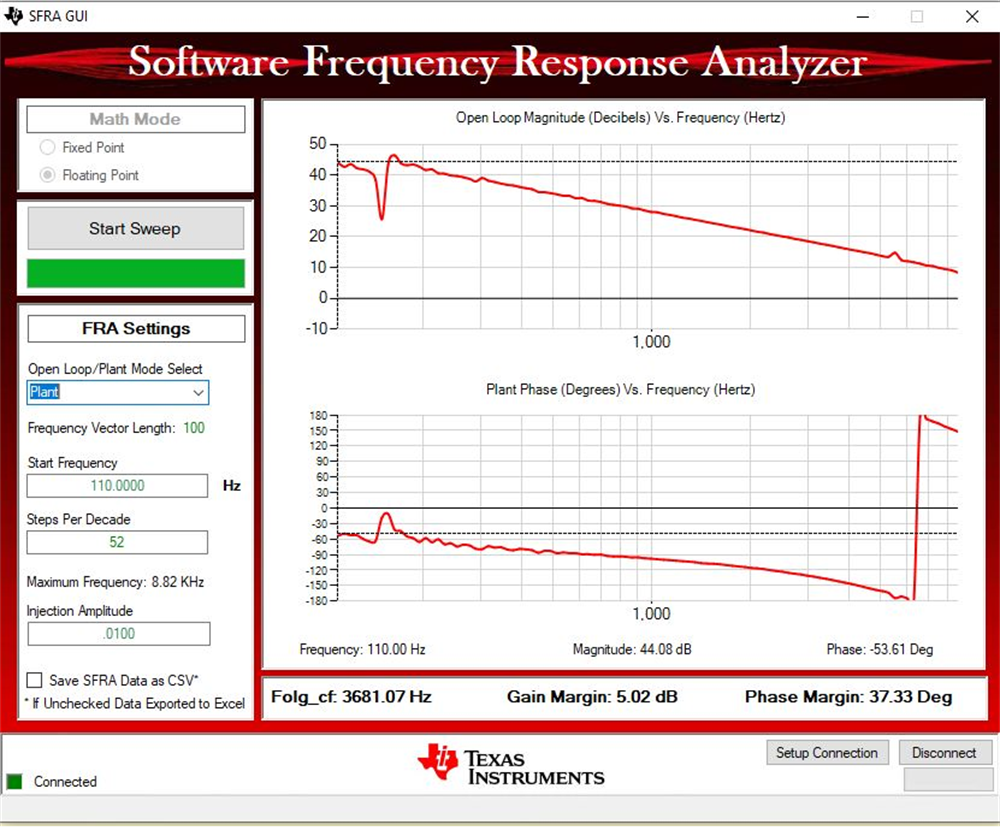

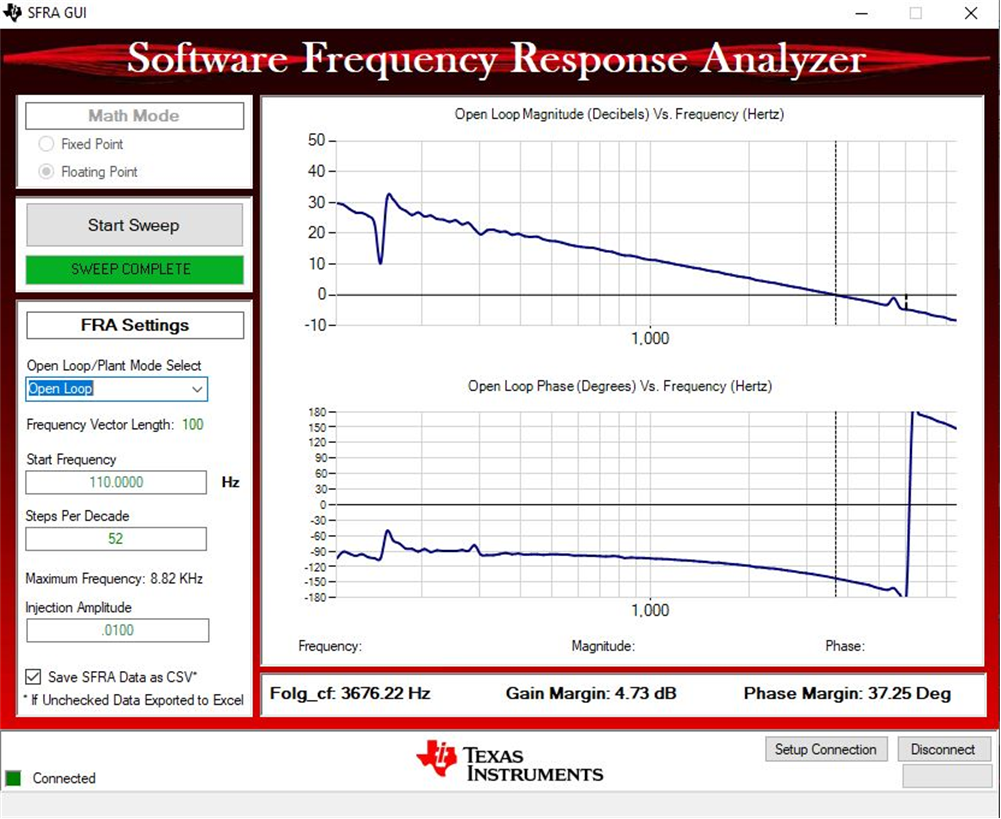

Measure the current loop bandwidth using SFRA. Figure 3-15 and Figure 3-16 show plant response and loop response of inverter operating in current mode measured on the HIL platform.

Figure 3-15 Inverter SFRA Plant Response Measured on HIL

Figure 3-15 Inverter SFRA Plant Response Measured on HIL Figure 3-16 Inverter SFRA Loop Response Measured on HIL

Figure 3-16 Inverter SFRA Loop Response Measured on HIL