JAJU510H March 2018 – December 2022

- 概要

- リソース

- 特長

- アプリケーション

- 5

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements, and Test Results

- 3.1 Required Hardware and Software

- 3.2 Testing and Results

- 4Design Files

- 5Trademarks

- 6About the Authors

- 7Revision History

3.2.5.1.1 PFC Start-up – 230 VRMS, 400 L-L AC Voltage

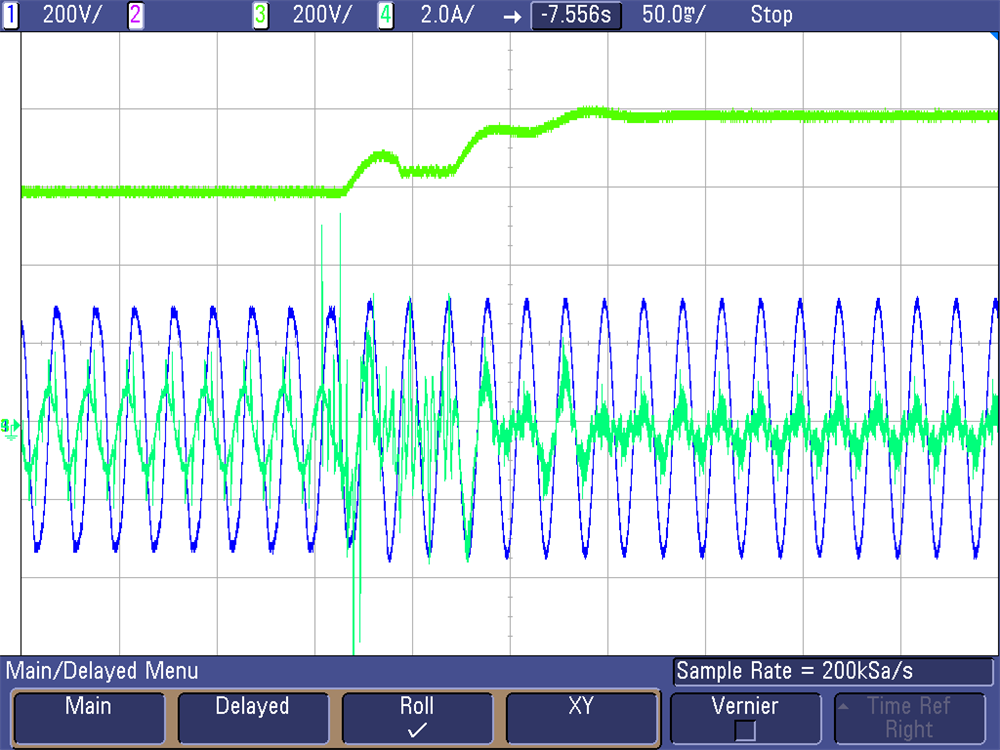

The start-up sequence of the power stage is shown in Figure 3-35 with input three phase 400- VL-L and output bus regulated at 800 V and a 245-W load. The boost action from 550 V to 800 V happens in around 140 ms. Figure 3-35 shows the start-up performance of PFC. Scope signals: Channel 1 - AC voltage (blue), Channel 2 - DC link voltage (light green), Channel 3 - AC current (dark green).

Figure 3-35 PFC 230 VRMS

Start-up

Figure 3-35 PFC 230 VRMS

Start-upCare has been taken in the tuning of voltage loop to ensure that there is no overvoltage (above 800 V) during the ramp up of DC link voltage from 550 V to 800 V at start-up. The bumps in the DC link voltage during this period is because the current implementation of d-q based control in software is not fully optimized for this. Also, starting the PFC at high load can lead to overcurrent events which in turn can trip the PWMs. Hence it is advisable to start the PFC in the above mentioned test condition or lower output power. Refer to Lab 5 on possible causes for PWM trip and possible precautions the user needs to take to avoid this condition.