JAJU809 march 2023

2.3.2.4 位相ノイズの最適化

アナログ信号チェーンの性能は、クロックの位相ノイズとジッタ性能に依存し、これらはデータ・コンバータの SNR、ENOB、SFDR に影響する可能性があります。このため、クロックの位相ノイズを最適化し、ジッタを最小限にします。

LMX2615-SP 最適化ループ・フィルタは、PLLatinum™ シミュレーション・ツールで、位相ノイズを最小化するようにプログラムできます。この設計では、ループ・フィルタは LMX2615-SP EVM コンポーネントと同じ状態に維持されます。

表 2-2 LMX2615-SP の設計パラメータ

| パラメータ | 値 |

|---|---|

| VCO ゲイン | 132MHz/V |

ループ帯域幅 | 285kHz |

位相マージン | 65° |

C1_LF | 390nF |

C2_LF | 68nF |

C3_LF | オープン |

C4_LF | 1.8nF |

R2 | 68Ω |

R3_LF | 0Ω |

R4_LF | 18Ω |

チャージ・ポンプ・ゲイン | 15mA |

位相検出器周波数 | 200MHz |

VCO 周波数 | 15GHz 向けに設計されていますが、全周波数範囲で動作します |

ADC の SNR は、外部クロックのジッタと内部 ADC のアパーチャ・ジッタにより低下します。ADC の SNR は、合計ジッタにより制限され、次のように計算されます。

式 1.

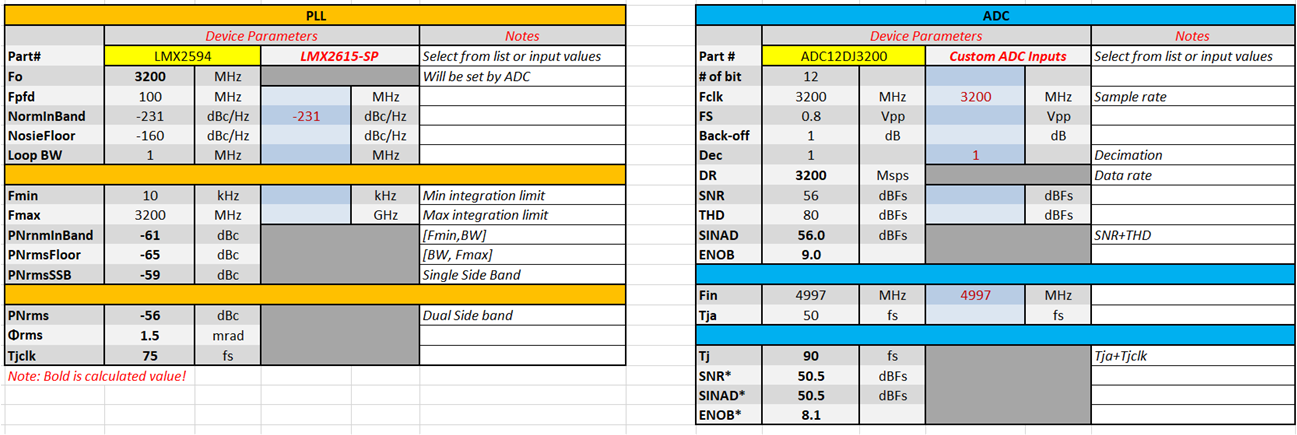

クロッキング性能に対する ADC12DJ3200-SP の SNR 性能を計算するため、テキサス・インスツルメンツは ADC 用のジッタおよび SNR カリキュレータを搭載したツールを提供しています (JITTER-SNR-CALC)。図 2-7 は、計算結果を含むスクリーンショットです。

図 2-7 ジッタから SNR へのツールのスクリーンショット

図 2-7 ジッタから SNR へのツールのスクリーンショット関連する SNR プロットを、図 2-8と 図 2-9 に示します。

図 2-8 SNR と TJ との関係

図 2-9 SNR と FIN との関係