SPRAD62 February 2023 F29H850TU , F29H859TU-Q1 , TMS320F280023C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038C-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- Abstract

- Trademarks

- 1Introduction

- 2Serial Port Design Methodology

- 3Example A: Using the CLB to Input and Output a TDM Stream in Audio Applications

- 4Example B: Using the CLB to Implement a Custom Communication Bus for LED Driver in Lighting Applications

- 5References

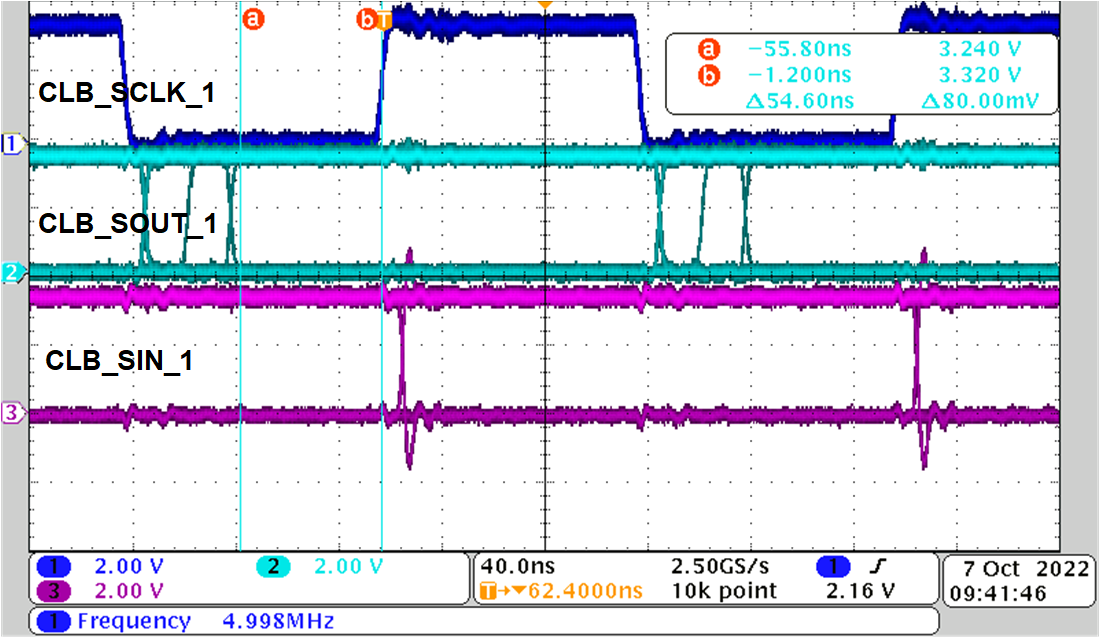

4.7.3 Testing Output Setup and Hold Times

A key consideration in the output CCSI bus from the CLB is the expected setup and hold time seen by the receiving device. To measure the setup and hold time, an oscilloscope was used to continuously capture the output of the CLB.

As shown in Figure 4-21, the CLB output has a minimum setup time of approximately 55 ns which is more than enough to meet the 10 ns setup time required by the LP5891-Q1 LED driver. Note the variation in the CLB_SOUT_1 output. As described in Section 4.6, this is due to the varying internal delays in updating the serializer output. The glitch can be eliminated by latching the serializer output before passing to CLB_SOUT. However, this method is not used given that the final output has enough setup time to meet the LP5891-Q1 LED driver requirements.

The hold time is at least half of an SCLK cycle.

Figure 4-21 LED Driver Example Setup and

Hold Time

Figure 4-21 LED Driver Example Setup and

Hold Time