SPRUIY9B May 2021 – October 2023

- 1

- Abstract

- Trademarks

- 1Key Features

- 2EVM Revisions and Assembly Variants

- 3Important Usage Notes

-

4System Description

- 4.1 Key Features

- 4.2 Functional Block Diagram

- 4.3 Power-On/Off Procedures

- 4.4

Peripheral and Major Component

Description

- 4.4.1 Clocking

- 4.4.2 Reset

- 4.4.3 Power

- 4.4.4 Configuration

- 4.4.5 JTAG

- 4.4.6 Test Automation

- 4.4.7 UART Interface

- 4.4.8 Memory Interfaces

- 4.4.9 Ethernet Interface

- 4.4.10 USB 3.0 Interface

- 4.4.11 PRU Connector

- 4.4.12 User Expansion Connector

- 4.4.13 MCU Connector

- 4.4.14 Interrupt

- 4.4.15 I2C Interface

- 4.4.16 IO Expander (GPIOs)

-

5Known Issues

- 5.1 Issue 1: LP8733x Max output Capacitance Spec Exceeded on LDO0 and LDO1

- 5.2 Issue 2: LP8733x Output Voltage of 0.9V Exceeds AM64x VDDR_CORE max Voltage Spec of 0.895 V

- 5.3 Issue 3 - SDIO Devices on MMC0 Require Careful Trace Lengths to Meet Interface Timing Requirements

- 5.4 Issue 4 - LPDDR4 Data Rate Limitation in Stressful Conditions

- 5.5 Issue 5 - Junk Character

- 5.6 Issue 6 - Test Power Down Signal Floating

- 5.7 Issue 7 - uSD Boot Not Working

- 6Regulatory Compliance

- 7Revision History

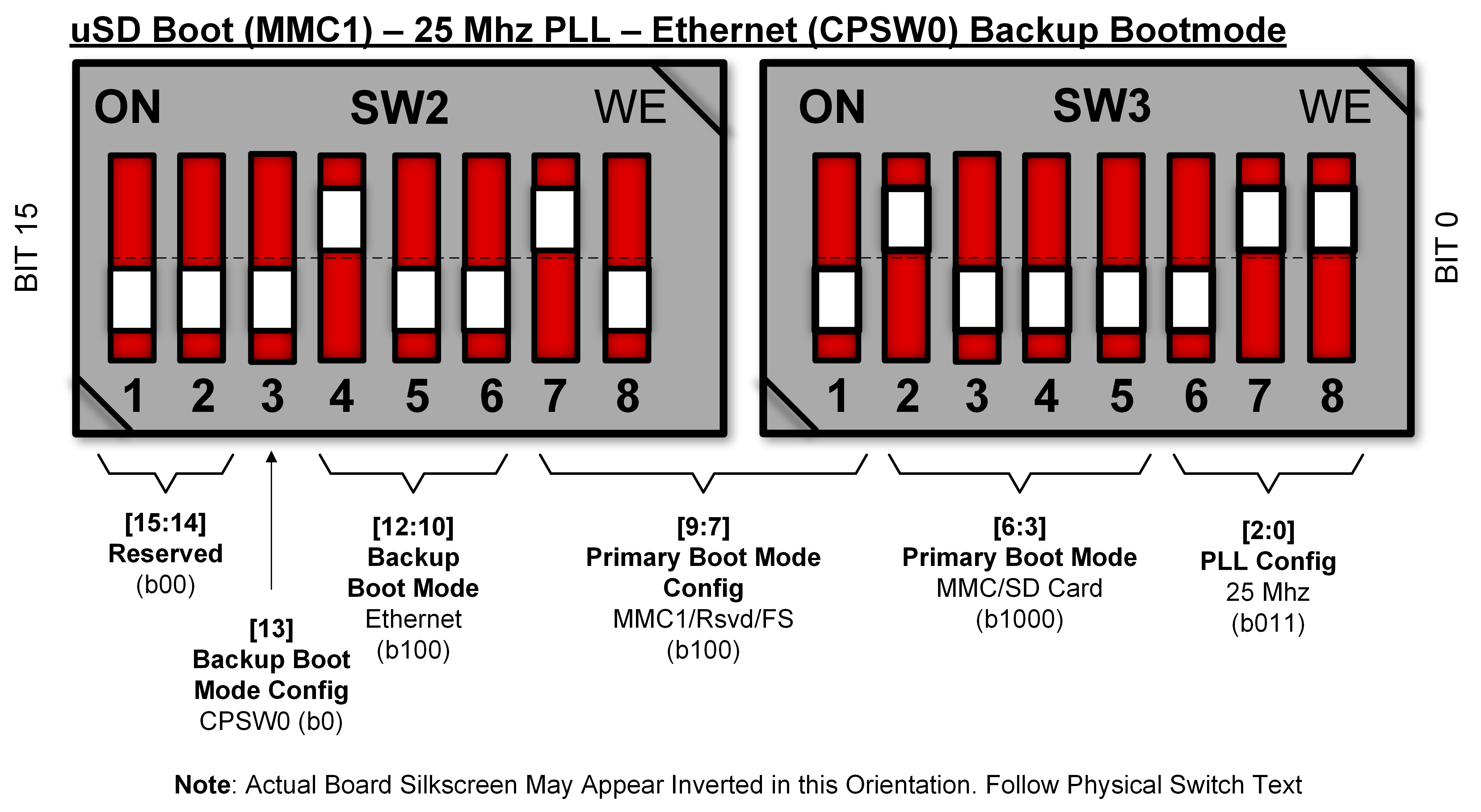

4.4.4.1 Boot Modes

The boot mode for the SK EVM board is defined by two banks of switches, SW2 and SW3, or by the I2C buffer connected to the test automation connector. This allows for AM64x boot mode control by either the user (DIP Switch Control) or the test automation header. At the minimum, all the boot mode pins require a footprint for a pull-up or pull-down resistor. Any boot mode pin that must be toggled to support a needed boot mode must have a weak pull-down resistor and a switch (416131160808 from Wurth) capable of connecting a stronger pull-up resistor. The switch disconnects the pull-up resistor in the OFF position. For boot mode pins that are not controlled by switches, pull-up and pull-down resistor pads are included. Various boot modes for AM64x must be controlled by the user with the help of 8-Bit DIP switches. The following boot modes are supported by SK EVM:

- OSPI

- MMC1 - SD-Card

- CSPW Ethernet

- USB devices

The boot mode pins of the SoC have associated alternate functions during normal operation. Hence, isolation is provided using the Buffer IC to cater for alternate pin functionality. The output of the buffer is connected to the bootmode pins ON the AM64x and the output is enabled when the bootmode is needed during a reset cycle. The input to the buffer is connected to the DIP switch circuit and to the output of an I2C buffer set by the test automation circuit. If the test automation circuit is going to control the bootmode, then all the switches are manually set to the OFF position. The bootmode buffer are powered by an always ON power supply to make sure that the bootmode remains present even if the SoC power is cycled..

Figure 4-10 and Table 4-7 provide guidance to select the boot mode before the device is powered up.

Figure 4-10 Bootmode Switch Positions

Example

Figure 4-10 Bootmode Switch Positions

Example| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Reserved | Reserved | Backup Boot Mode Configuration | Backup Boot Mode | Primary Boot Mode Configuration | Primary Boot Mode | PLL Configuration | |||||||||

• BOOT-MODE [0:2] – Denote system clock frequency for PLL configuration. By default, this bits are set for 25 MHz.

Table 4-8 gives details ON PLL reference clock selection.

| SW3.6 | SW3.7 | SW3.8 | PLL REF CLK (MHz) |

|---|---|---|---|

| OFF | OFF | OFF | 19.2 |

| OFF | OFF | ON | 20 |

| OFF | ON | OFF | 24 |

| OFF | ON | ON | 25 |

| ON | OFF | OFF | 26 |

| ON | OFF | ON | 27 |

| ON | ON | OFF | Reserved |

| ON | ON | ON | No PLL Configuration Done (slow speed backup) |

• BOOT-MODE [3:6] – This provides primary boot mode configuration to select the requested boot mode after POR, that is, the peripheral/memory to boot from. Table 4-9 provides primary boot device selection details.

| SW3.2 | SW3.3 | SW3.4 | SW3.5 | Primary Boot Device Selected |

|---|---|---|---|---|

| OFF | OFF | OFF | OFF | Reserved |

| OFF | OFF | OFF | ON | OSPI |

| OFF | OFF | ON | OFF | QSPI |

| OFF | OFF | ON | ON | SPI |

| OFF | ON | OFF | OFF | Ethernet RGMII |

| OFF | ON | OFF | ON | Ethernet RMII |

| OFF | ON | ON | OFF | I2C |

| OFF | ON | ON | ON | UART |

| ON | OFF | OFF | OFF | MMC/SD card |

| ON | OFF | OFF | ON | emmc |

| ON | OFF | ON | OFF | USB |

| ON | OFF | ON | ON | Reserved |

| ON | ON | OFF | OFF | GPMC NOR |

| ON | ON | OFF | ON | PCIe |

| ON | ON | ON | OFF | xSPI |

| ON | ON | ON | ON | No boot/Dev Boot |

• BOOT-MODE [10:12] – Select the backup boot mode, that is, the peripheral/memory to boot from, if primary boot device failed.

Table 4-10 provides backup boot mode selection details.

| SW2.4 | SW2.5 | SW2.6 | Backup Boot Device Selected |

|---|---|---|---|

| OFF | OFF | OFF | None (No backup mode) |

| OFF | OFF | ON | USB |

| OFF | ON | OFF | Reserved |

| OFF | ON | ON | UART |

| ON | OFF | OFF | Ethernet |

| ON | OFF | ON | MMC/SD |

| ON | ON | OFF | SPI |

| ON | ON | ON | I2C |

• BOOT-MODE [9:7] – These pins provide optional settings and are used in conjunction with the primary boot device selected.

Table 4-11 gives primary boot media configuration details.

| SW2.7 | SW2.8 | SW3.1 | Boot Device |

|---|---|---|---|

| Reserved | Reserved | ||

| Speed | Iclk | Csel | OSPI |

| Reserved | Iclk | Csel | QSPI |

| Reserved | Mode | Csel | SPI |

| Clkout | Delay | Link stat | Ethernet RGMII |

| Clkout | Clk src | Reserved | Ethernet RMII |

| Bus Reset | Reserved | Addr | I2C |

| Reserved | Reserved | UART | |

| Port | Reserved | Fs/raw | MMC/ SD card |

| Reserved | voltage | eMMC | |

| Reserved | Mode | Lane swap | USB |

| Reserved | Reserved | ||

| Reserved | GPMC NOR | ||

| Reserved | Clocking | PCIe | |

| Speed | Pin Cmd | Csel | xSPI |

| Reserved | No/Dev | No boot/Dev Boot | |

• BOOT-MODE [13] – These pins provide optional settings and are used in conjunction with the backup boot device devices. Switch SW2.6 when ON sets 1 and sets 0 if OFF, see the device-specific TRM.

• BOOT-MODE [14:15] – Reserved.

Table 4-12 provides backup boot media configuration options.

| SW2.3 | Boot Device |

|---|---|

| Reserved | None |

| Mode | USB |

| Reserved | Reserved |

| Reserved | UART |

| IF | Ethernet |

| Port | MMC/SD |

| Reserved | SPI |

| Reserved | I2C |