SPRUJ09D March 2022 – September 2023 AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P2-Q1 , AM263P4 , AM263P4-Q1

- 1

- Abstract

- Trademarks

- 1Preface: Read This First

- 2Control Card Overview

- 3Board Setup

- 4Hardware Description

- 5References

- Revision History

- A E2 Design Changes

- B E1 HSEC Pinout Table

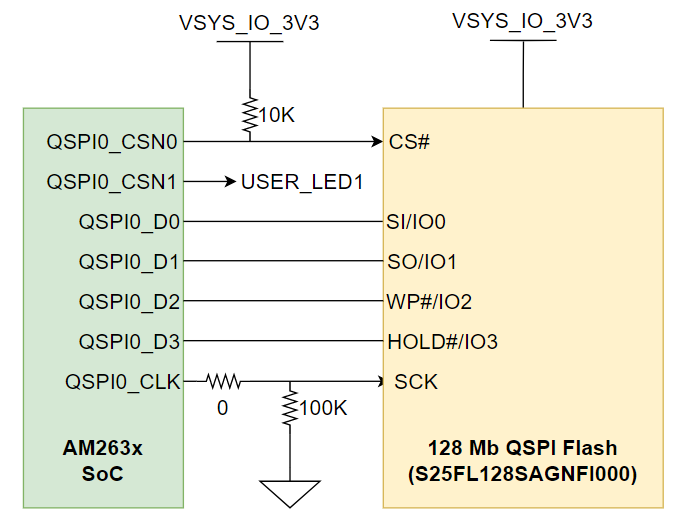

4.5.1 QSPI

The AM263x Control Card has a 128Mbit QSPI memory device (S25FL128SAGNFI000), which is connected to the QSPI0 interface of the AM263x SoC. The QSPI interface supports single data rates with memory speeds up to 104 MHz. The QSPI flash is powered by the 3.3-V IO supply.

Note: There is typically a reset pin

for Flash memory. The Reset pin is not present in the WSON package that is used

in the Control Card.

The QSPI0_D0/D1 signals are also used for BOOTMODE control logic. There are 10-kΩ resistors used to isolate the BOOTMODE control logic after the value is latched.

Figure 4-7 QSPI Interface

Figure 4-7 QSPI Interface