SPRUJ09D March 2022 – September 2023 AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P2-Q1 , AM263P4 , AM263P4-Q1

- 1

- Abstract

- Trademarks

- 1Preface: Read This First

- 2Control Card Overview

- 3Board Setup

- 4Hardware Description

- 5References

- Revision History

- A E2 Design Changes

- B E1 HSEC Pinout Table

A E2 Design Changes

The AM263x Control Card had various design changes for the E2 revision of the board. The changes are listed below:

- Removal of pull up resistors

for QSPI flash D2 and D3 signals.

- The pull up resistors on the data lines D2 and D3 are redundant with the on-die resistors of the QSPI flash itself.

- Fixed netlist error and

rerouted I2C2_SDA and I2C2_SCL for proper operation.

- The E1 revision of the

Control Card had the I2C2_SCL signal tied to ball B7 and I2C2_SDA tied

to C7. The correct routing of the signals is implemented in the E2

Control Card with I2C2_SDA connected to B7 and I2C2_SCL connected to

C7.Table A-1 I2C2 Signal Routing

Signal E1 Pin Routing E2 Pin Routing I2C2_SDA C7 B7 I2C2_SCL B7 C7

- The E1 revision of the

Control Card had the I2C2_SCL signal tied to ball B7 and I2C2_SDA tied

to C7. The correct routing of the signals is implemented in the E2

Control Card with I2C2_SDA connected to B7 and I2C2_SCL connected to

C7.

- Ethernet PHY default mode

changed to enhanced mode from basic mode.

- The Ethernet PHY (DP83826ERHBT) in E1 had a default mode of basic due to a pull down resistor on the MODESELECT pin of the PHY. E2 replaced the pull down with a pull up resistor so that the default mode would be enhanced mode. Enhanced mode allows for the PHY to support real time Ethernet applications.

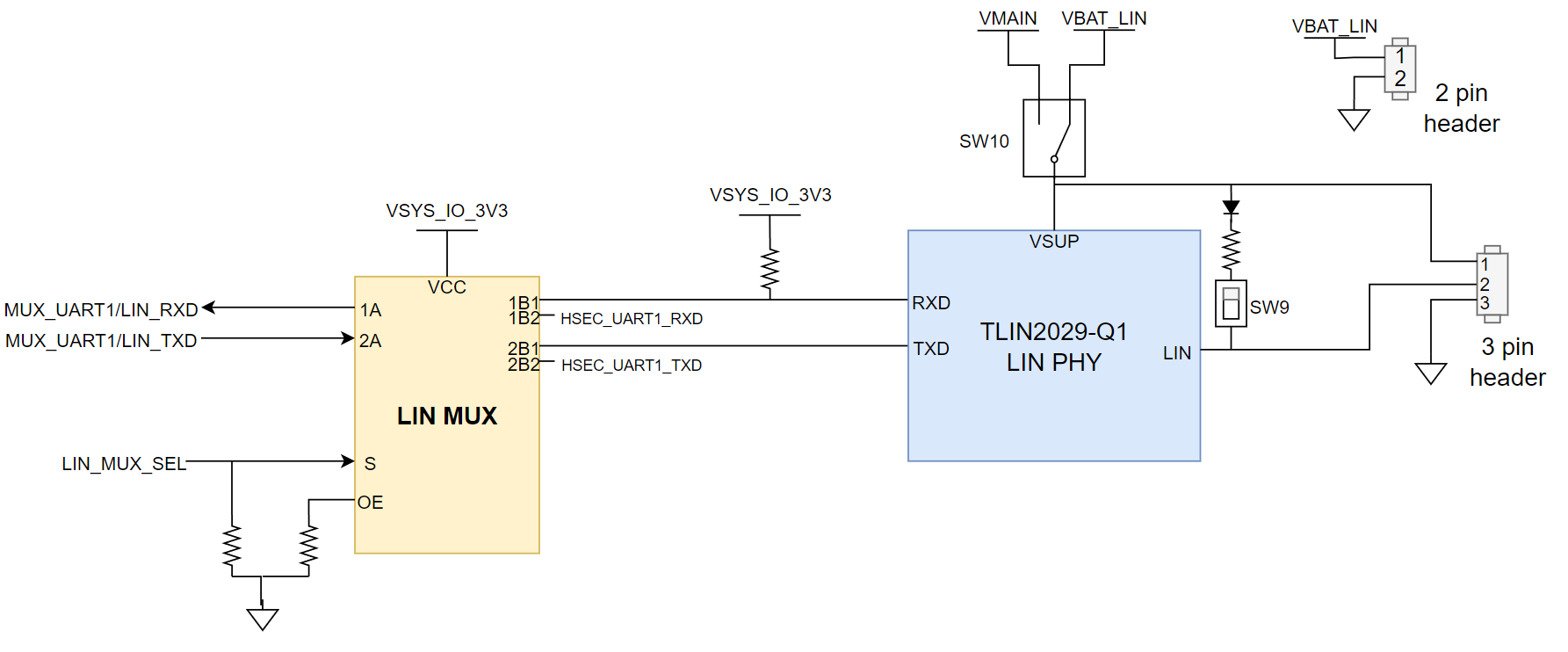

- Add on-board LIN PHY

(TLIN2029-Q1).

- In order to support the LIN PHY, a 1:2 mux (U70) was added so that the LIN1_RXD and LIN1_TXD would be able to interface with the PHY without losing the signal pathing for UART1_RXD and UART1_TXD.

- Two additional header

were added to support the LIN PHY's voltage (J33) and output (J32) Table A-2 LIN MUX Selection Table

Select Line Condition Function LOW LIN Selected A->B1 port HIGH HSEC UART Selected A->B2 port  Figure A-1 LIN

PHY

Figure A-1 LIN

PHY

- Added

additional series termination resistors.

- 33Ω resistors were placed for the XDS110 TMS and TCK signals at the output of an isolation buffer (U49). One 33Ω resistor was placed for the XDS110 TDI signal on the OUTA of an isolation buffer (U53).

- Series terminations

resistors were places on outputs of three isolation buffers to better

control edge overshoot/undershoot. Table A-3 E2 Termination Resistor Location Table

Isolation Buffer Output Pin Signal Name Series Termination Resistor Value U45.2 UART0_RXD 33Ω U49.6 XDS110_TCK_ISO 33Ω U49.7 XDS110_TMS_ISO 33Ω U53.2 XDS110_TDI_ISO 33Ω

- DC-DC converter solution

components updated.

- The DC-DC buck converters

responsible for generating the 3.3V rail and 1.2V rail were both

replaced with the TSP62913RPUR buck converter. Table A-4 E2 Buck Converter Table

DC-DC Conversion E1 Buck Converter E2 Buck Converter 5V->3.3V TPS54334DRCT TPS62913RPUR 3.3V->1.2V TPS62826DMQR TPS62913RPUR

- The DC-DC buck converters

responsible for generating the 3.3V rail and 1.2V rail were both

replaced with the TSP62913RPUR buck converter.

- Updated passive

components.

- C136 and C1861 were replaced with 0805 from 1210

- L3 and L4 were replaced with IHLP2020BZER1R0M01 from 744316100

- Changed HSEC ADC

Connections.Table A-5 E2 HSEC Connector Mapping

HSEC Pin E1 Signal E2 Signal 1 NC NC 2 NC NC 3 TMS TMS 4 NC NC 5 TCK TCK 6 TDO TDO 7 GND GND 8 TDI TDI 9 DAC_OUT ADC0_AIN0/DAC_OUT 10 GND GND 11 ADC0_AIN0_P ADC0_AIN1/DAC_OUT 12 ADC0_AIN0_n ADC1_AIN0 13 GND GND 14 ADC0_AIN1_p ADC1_AIN1 15 ADC0_AIN1_n ADC0_AIN2 16 GND GND 17 ADC0_AIN2_p ADC0_AIN3 18 ADC0_AIN2_n ADC1_AIN2 19 GND GND 20 ADC1_AIN0_p ADC1_AIN3 21 ADC1_AIN0_n ADC0_AIN4 22 GND GND 23 ADC1_AIN1_p ADC0_AIN5 24 ADC1_AIN1_n ADC1_AIN4 25 ADC1_AIN2_p ADC4_AIN0/ADC_CAL0 26 ADC1_AIN2_n ADC1_AIN5 27 ADC2_AIN0_p ADC4_AIN1/ADC_CAL1 28 ADC2_AIN0_n ADC3_AIN0 29 GND GND 30 ADC2_AIN1_p ADC3_AIN1 31 ADC2_AIN1_n ADC2_AIN0 32 NC GND 33 ADC2_AIN2_p ADC2_AIN1 34 ADC2_AIN2_n ADC3_AIN2 35 GND GND 36 ADC3_AIN0_p ADC3_AIN3 37 ADC3_AIN0_n ADC2_AIN2 38 GND GND 39 ADC3_AIN1_p ADC2_AIN3 40 ADC3_AIN1_n ADC3_AIN4 41 NC NC 42 ADC3_AIN2_p ADC3_AIN5 43 ADC_VREFLO GND 44 NC NC 45 ADC_VREFhi ADC_VREFH Table A-6 E1 ADC Channel SignalsADC0 AIN0p AIN0n AIN1p AIN1n AIN2p AIN2n ADC1 AIN0p AIN0n AIN1p AIN1n AIN2p AIN2n ADC2 AIN0p AIN0n AIN1p AIN1n AIN2p AIN2n ADC3 AIN0p AIN0n AIN1p AIN1n AIN2p GND ADC4 GND GND GND GND GND GND Table A-7 E2 ADC Channel SignalsADC0 AIN0 AIN1 AIN2 AIN3 AIN4 AIN5 ADC1 AIN0 AIN1 AIN2 AIN3 AIN4 AIN5 ADC2 AIN0 AIN1 AIN2 AIN3 GND GND ADC3 AIN0 AIN1 AIN2 AIN3 AIN4 AIN5 ADC4 AIN0 AIN1 GND GND GND GND - Added

two 2:1 MUX's to support new HSEC ADC Connections.Table A-8 E2 HSEC MUX Table

MUX_SEL Signal Condition Function Description ADC1_MUX_SEL SEL Signal HIGH S1A->D1 route HSEC_ADC0_AIN0 to AM263 S2A->D2 route HSEC_ADC0_AIN1 to AM263 SEL Signal LOW S1B->D1 route HSEC_DAC_OUT to AM263 S2B->D2 route HSEC_DAC_OUT to AM263 ADC2_MUX_SEL SEL Signal HIGH S1A->D1 route HSEC_ADC4_AIN0 to AM263 S2A->D2 route HSEC_ADC4_AIN1 to AM263 SEL Signal LOW S1B->D1 route ADC_CAL0 to AM263 S2B->D2 route ADC_CAL0 to AM263 - Updated ADC ESD Connections.

Table A-9 E2 ESD Connection Mapping

E1 ESD Pin E1 Signal E2 ESD Pin E2 Signal U26.1 HSEC_ADC0_AIN0_P U35.1 HSEC_ADC0_AIN0/DAC_OUT U26.2 GND U35.2 GND U26.3 HSEC_ADC0_AIN0_N U35.3 HSEC_ADC0_AIN1/DAC_OUT U26.4 HSEC_ADC0_AIN1_N U35.4 HSEC_ADC4_AIN0/ADC_CAL0 U26.5 VDDA_IO_1V8 U35.5 VDDA_IO_3V3 U26.6 HSEC_ADC0_AIN1_P U35.6 HSEC_ADC4_AIN1/ADC_CAL1 U27.1 HSEC_ADC0_AIN2_P U36.1 HSEC_ADC1_AIN0 U27.2 GND U36.2 GND U27.3 HSEC_ADC0_AIN2_N U36.3 HSEC_ADC1_AIN1 U27.4 HSEC_ADC1_AIN0_N U36.4 HSEC_ADC0_AIN3 U27.5 VDDA_IO_1V8 U36.5 VDDA_IO_3V3 U27.6 HSEC_ADC1_AIN0_P U36.6 HSEC_ADC0_AIN2 U28.1 HSEC_ADC1_AIN1_P U37.1 HSEC_ADC2_AIN0 U28.2 GND U37.2 GND U28.3 HSEC_ADC1_AIN1_N U37.3 HSEC_ADC2_AIN1 U28.4 HSEC_ADC1_AIN2_N U37.4 HSEC_ADC0_AIN5 U28.5 VDDA_IO_1V8 U37.5 VDDA_IO_3V3 U28.6 HSEC_ADC1_AIN2_P U37.6 HSEC_ADC0_AIN4 U29.1 HSEC_ADC2_AIN0_P U38.1 HSEC_ADC3_AIN0 U29.2 GND U38.2 GND U29.3 HSEC_ADC2_AIN0_N U38.3 HSEC_ADC3_AIN1 U29.4 HSEC_ADC2_AIN1_N U38.4 HSEC_ADC3_AIN3 U29.5 VDDA_IO_1V8 U38.5 VDDA_IO_3V3 U29.6 HSEC_ADC2_AIN1_P U38.6 HSEC_ADC3_AIN2 U30.1 HSEC_ADC2_AIN2_P U39.1 HSEC_ADC3_AIN4 U30.2 GND U39.2 GND U30.3 HSEC_ADC2_AIN2_N U39.3 HSEC_ADC3_AIN5 U30.4 HSEC_ADC3_AIN0_N U39.4 HSEC_ADC2_AIN3 U30.5 VDDA_IO_1V8 U39.5 VDDA_IO_3V3 U30.6 HSEC_ADC3_AIN0_P U39.6 HSEC_ADC2_AIN2 U31.1 HSEC_ADC3_AIN1_P U40.1 HSEC_ADC1_AIN2 U31.2 GND U40.2 GND U31.3 HSEC_ADC3_AIN1_N U40.3 HSEC_ADC1_AIN3 U31.4 HSEC_ADC3_AIN2_P U40.4 HSEC_ADC1_AIN4 U31.5 VDDA_IO_1V8 U40.5 VDDA_IO_3V3 U31.6 NC U40.6 HSEC_ADC1_AIN5