SBAU411 February 2023 ADS127L21

6.7 Digital Filter Configuration

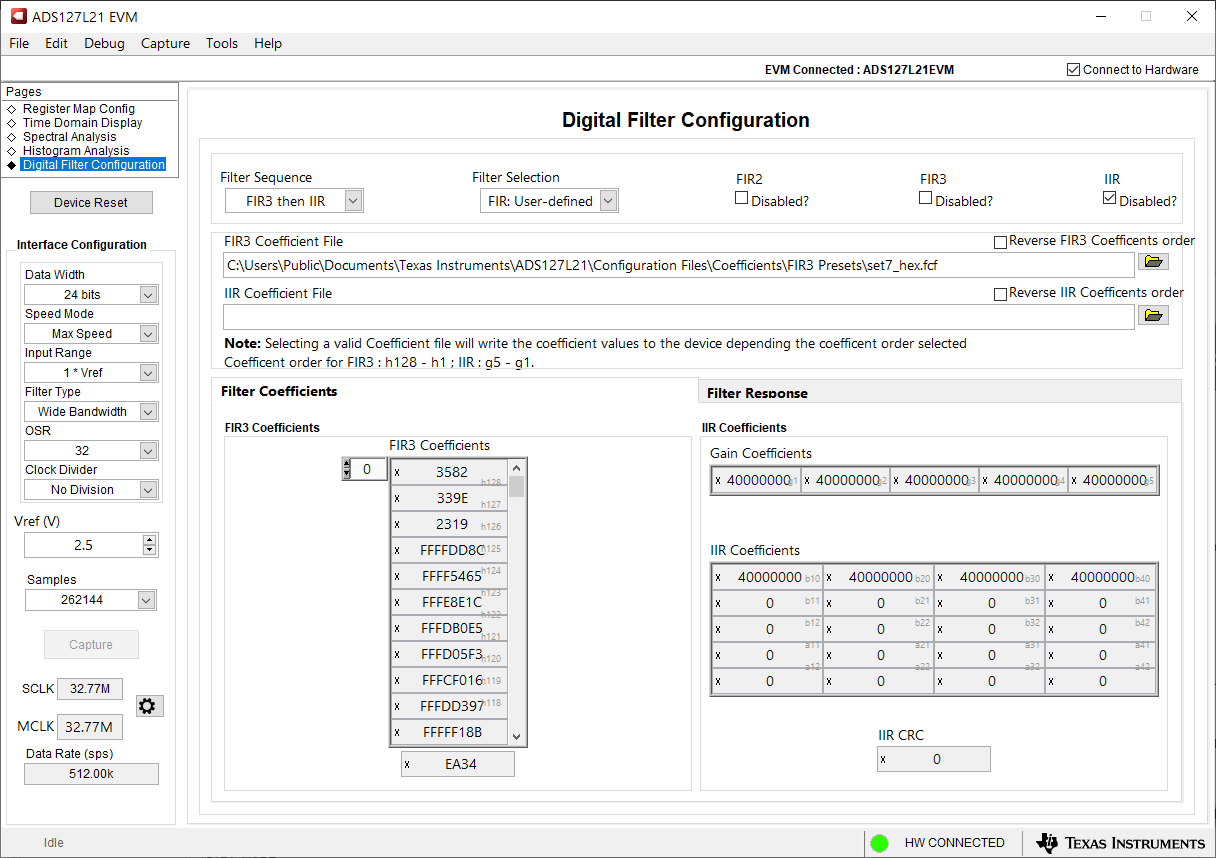

The Digital Filter Configuration page allows loading of custom digital filters into both the FIR and IIR programmable filter registers inside the ADS127L21 ADC. These filters are designed in separate tools, such as MATLAB®, and the coefficients can be viewed and transferred to the ADS127L21 filter registers. There are several options to enable or disable different filter stages inside the ADS127L21; see the ADS127L21 data sheet for details. As shown in #GUID-84B4427D-0752-4294-B66C-EFA76E7CB64C, the Filter Sequence, Selection, and Type can be selected. FIR and IIR coefficient files can also be loaded and the values can be viewed.

Figure 6-8 Digital Filter

Configuration

Figure 6-8 Digital Filter

Configuration