SPRAC77E January 2022 – February 2022 TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S

- Trademarks

- 1Introduction

- 2PTO – PulseGen

- 3PTO – QepDiv

- 4PTO – Abs2Qep

- 5PTO – QepOnClb QEP Decoder

- 6Example Projects

- 7Library Source and Projects

- 8Using the Reference APIs in Projects

- 9References

- Revision History

4.3.2 Abs2Qep Halt Latch

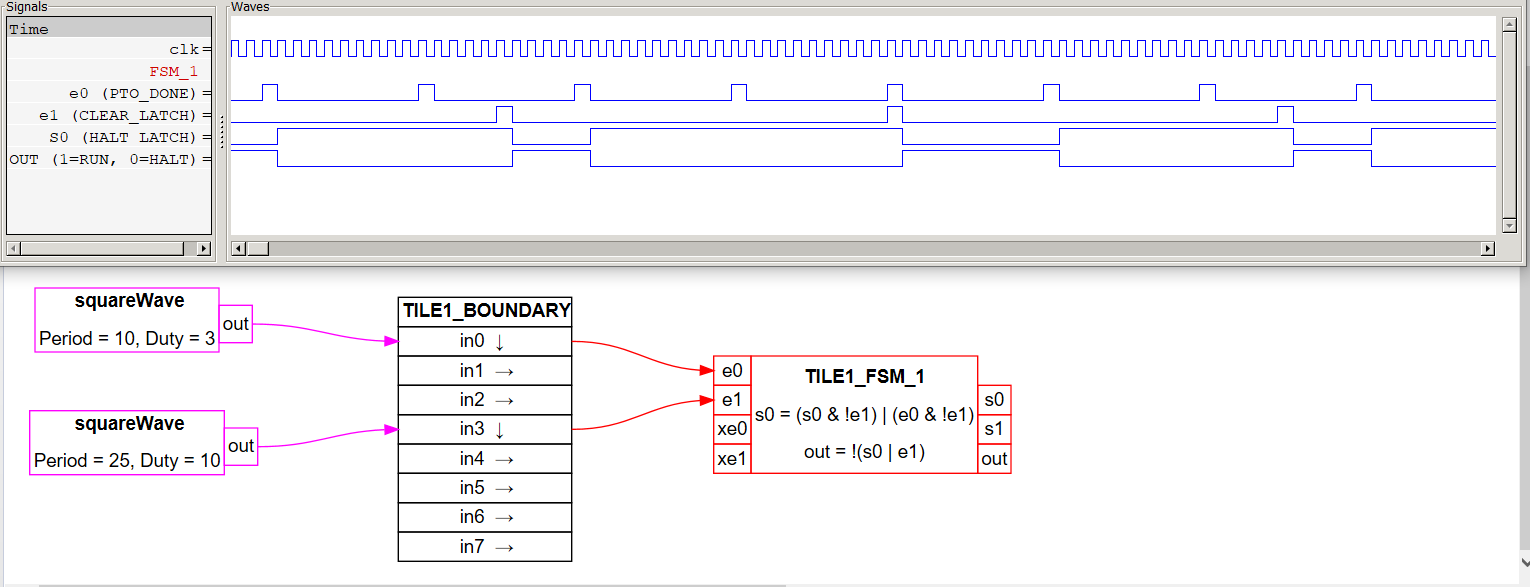

The HALT_LATCH and RUN/HALT output is implemented using a finite state machine. The output signal is connected to the mode0 input of the counter which generates QCLK. The RUN/HALT output depends only on the current state of the latch and the HALT signal from the CPU. If the HALT signal is low, and the latch is not set, then QCLK will be generated (COUNTER mode0 = out = 1). In all other cases QCLK will not be generated (COUNTER mode0 = out = 0). This is expressed as out = !(s0 | e1).

| s0 (LATCH) |

e1 (HALT/CLEAR LATCH) |

out = !(s0|e1) | QCLK Generation |

|---|---|---|---|

| 0 | 0 | 1 | Run |

| 0 | 1 | 0 | Halt |

| 1 | 0 | 0 | Halt |

| 1 | 1 | 0 | Halt |

HALT_LATCH is set on the rising edge of PTO_DONE. It will remain set until cleared by a a rising edge on the HALT/CLEAR_LATCH signal from the CPU.

| PTO_DONE, CLEAR_LATCH (e0, e1) | |||||

| 00 | 01 | 11 | 10 | ||

| s0 (LATCH) |

0 | 0 | 0 | 0 | 1 (2) |

| 1 | 1 (1) | 0 | 0 | 1 (1),(2) | |

The Halt Latch SystemC simulation is shown in Figure 4-10.

Figure 4-10 Simulation of Halt Latch

Figure 4-10 Simulation of Halt Latch