JAJA750A november 2021 – december 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

4.3 部品の配置

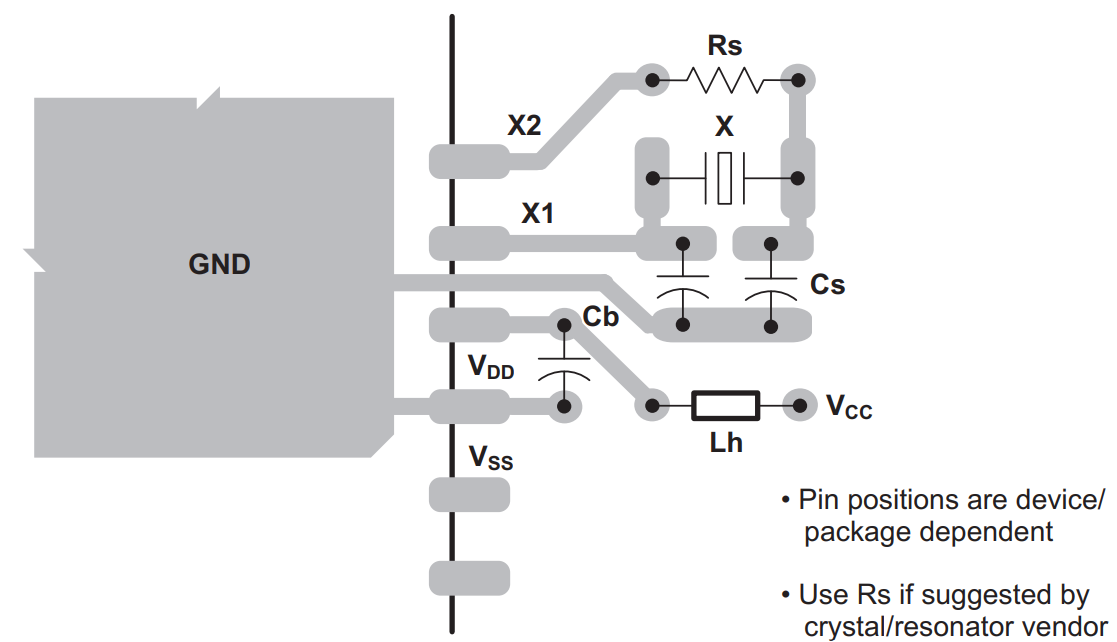

ボード上の C2000 チップの位置を決定したら、次に水晶振動子 / 発振器を配置します。これは、クロックを最も効率的に供給できるように、できる限りデバイスの近くに配置する必要があります。具体的には、X1/X2 へのトレースはできるだけ短くします。使用する水晶振動子に必要な追加部品によって、水晶振動子 / 共振器を基板上に配線する方法は異なります。図 4-4 に、2 層基板と、追加の直列抵抗 Rs を必要とする水晶振動子を配置した例を示します。クロック・トレースを 1 つのデバイスから別のデバイスに配線するときは、3W 間隔ルールを使用してみてください。クロック・トレースの中心から隣接する信号トレースの中心までの距離は、クロック・トレースの幅の 3 倍以上にする必要があります。多くのクロックは、低速周波数クロックも含め、立ち上がり時間と立ち下がり時間が高速である場合があります。3W ルールを使用すると、トレース間のクロストークを削減できます。一般に、デバイス間で並列に動作する各トレースの間に間隔を確保してください。配線距離とインピーダンスの不連続性を最小限に抑えるため、トレースを配線するときには直角に曲げることは避けてください。クロストークからさらに保護するため、可能な場合はクロック信号の横にガード・トレース (GND ピンから GND ピン) を配置します。これにより、クロック信号の結合が減少します。

図 4-4 推奨される発振器のレイアウト

図 4-4 推奨される発振器のレイアウト次に配置する重要な部品は、デカップリング / バイパス・コンデンサです。これらのコンデンサは、それぞれのピンのできるだけ近くに配置する必要があります。これらのコンデンサは、ノイズをさらに低減し、デバイスの電源を安定させるのに役立ちます。ピンから 1 インチ以上離れた場所にデカップリング・コンデンサを配置すると、性能が低下します。バルク・コンデンサは、チップから比較的離れた場所に配置しても、性能に大きな影響を及ぼすことはありません。図 4-5 に、デカップリング・コンデンサの適切な配置を示します。

図 4-5 基板レイアウトのデカップリング・コンデンサ

図 4-5 基板レイアウトのデカップリング・コンデンサこの後に、JTAG ヘッダー / 回路と XRSn 回路を配置します。

TMS320F28004x デバイスの内部 1.2V DC/DC レギュレータを使用するシステムでは、DC/DC 回路を適切に設計するため、以下のガイドラインに従ってください。

- VDDIO_SW および VDDIO は、同じ 3.3V 電源にスター接続することを推奨します。

- すべての外付け部品は、できるだけピンに近付けて配置してください。

- VDDIO _SW、入力コンデンサ (CVDDIO_SW)、および VSS_SW によって形成されるループは、できるだけ短くする必要があります。

- 帰還パターンはできるだけ短くし、スイッチング出力 (VSW) などのノイズ源から離して配置する必要があります。

- 入力コンデンサ (CVDDIO_SW) および VSS_SW のグランド・プレーンには、独立したアイランドまたは切り込みが必要です。

- 寄生抵抗とインダクタンスを最小限に抑えるために、VDD ノードの LVSW-CVDD ポイントへの接続には、VDD プレーンを推奨します。