JAJA750A november 2021 – december 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

4.4 グランド・プレーン

PCB 上の銅プレーンは優れた高周波コンデンサであり、推奨されるコンデンサとともに、高周波バイパスに使用できます。固体プレーンのもう 1 つの利点は、良好なヒートシンクとして機能し、過剰な熱レベルを下げることができることです。

基板の層が大きい場合は、PCB 上にグランドを配置することをお勧めします。グランド・プレーンは、基板上のグランド信号を配線しやすくするだけでなく、グランド・ノイズの低減にも役立ちます。基板上の各信号にはリターン電流 (GND 経由) があり、これにより、リターン・パスが最小インピーダンスのパスを通過するようになります。異なる層に複数のグランド・プレーンを持つ基板の場合、ビア・スティッチングを使用してこれらのグランド・プレーンを接続すると、インピーダンスをさらに低減できます。リターン・パスの詳細については、『高速レイアウト・ガイドライン』の「リターン電流およびループ領域」セクションを参照してください。

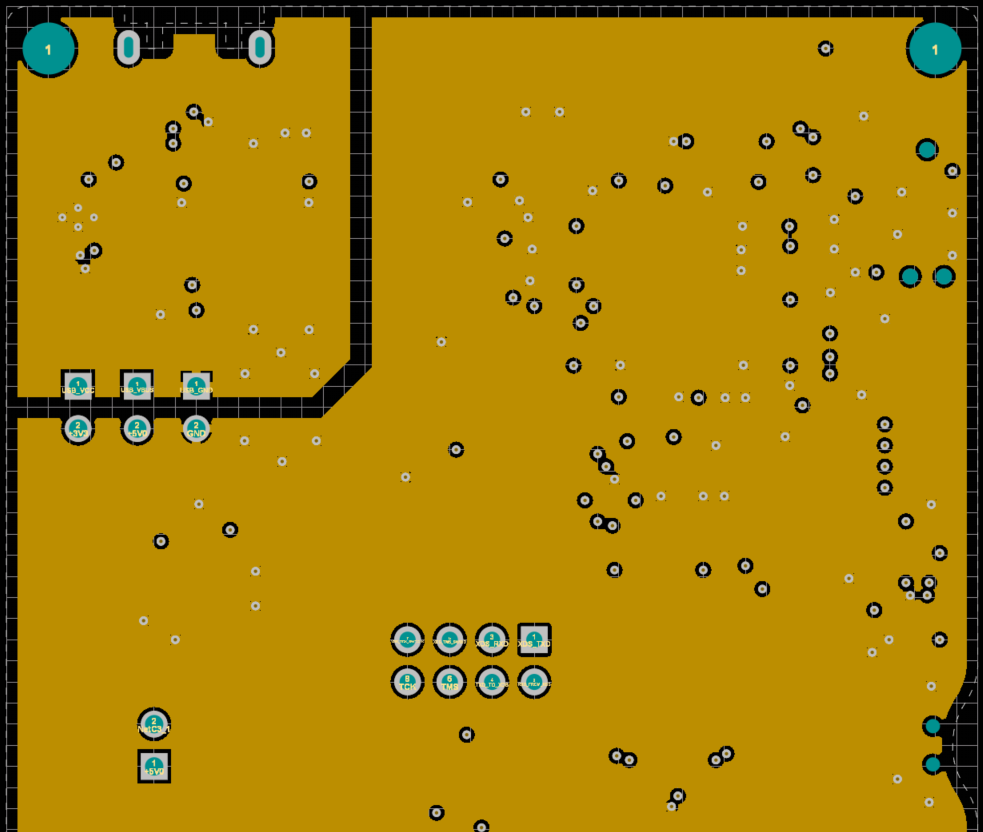

図 4-7 LaunchPad のグランド・プレーン

図 4-7 LaunchPad のグランド・プレーン効果的なグランド・プレーンのために重要となるのは、プレーンがそのまま維持され、基板の層全体にわたって良好な接続があるようにすることです。ビアやトレースなどのオンボード接続により、グランド層が切断され、効果が低減されることがあります。ビアは基板の複数の層を貫通する穴を作成し、トレースはグランド・プレーンの複数の部分の間の接続を遮断する可能性があります。下の左の図では、PGND ビアはグランド・プレーンに 1 つの接続のみを持ち、周囲のグランド・ポア接続は非常に幅が狭くなっています。また、図 4-8 では、ポアの左上が幅の狭い銅を介してポアの左下に接続されています。これらの図はどちらも、望ましくないグランド・プレーンの例を示しています。ビアとトレースを再配置して、幅の狭いグランド・プレーン接続がなく、グランド・ポアが切断されないていないことを確認すると有益です。

図 4-8 グランド・プレーン切断の例

図 4-8 グランド・プレーン切断の例グランド・プレーンを層に適用する場合は、プレーン全体で良好な接続が得られることを確認します。プレーンが不足している領域や接続の幅が狭い領域を再設計し、グランド・プレーン領域を最大化する必要があります。通常これは、ビアの数を減らし、トレースのグループを近づけて配線することで達成できます。場合によっては、PinMux での選択と回路図を変更して、配線を改善すると役立つことがあります。これらの利点がレイアウトの配線プロセスを開始するまで明らかにならない場合もありますが、PinMux を最適化すると、トレース長が短くなり、ビアの使用量が削減されるため、グランド・プレーンが向上する可能性があります。