JAJA750A november 2021 – december 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

3.2.4 通信ペリフェラル

F2800x デバイスには、さまざまな数の以下の通信ペリフェラルが搭載されています。

- CAN (Controller Area Network) / DCAN

- モジュラー・コントローラ・エリア・ネットワーク (MCAN/CAN FD)

- I2C (Inter-Integrated Circuit)

- PMBus (Power Management Bus) インターフェイス

- シリアル通信インターフェイス (SCI)

- シリアル・ペリフェラル・インターフェイス (SPI)

- LIN (Local Interconnect Network)

- 高速シリアル・インターフェイス (FSI)

- ホスト・インターフェイス・コントローラ (HIC)

これら全てのペリフェラルはそれぞれ異なるプロトコルで通信を行うので、意図した通信ペリフェラルのサポートを考慮して各システムを設計する必要があります。I2C、PMBus、SPI を含むボード・レベルのインターフェイスは、ボード上またはシステム経由で他のデバイスに接続されています。通常これらのドライバは直接駆動されるため、駆動能力とトレース長に十分注意してください。これらの要因は、これらの信号の選択した周波数によって異なります。

CAN を使用する場合、内部発振器を使用するのではなく、外部発振器を基板に実装することを推奨します。ビットのタイミング設定、ビット・レート、バス長、伝搬遅延などの必要な CAN パラメータによって、オンチップ・ゼロ・ピン発振器の精度が CAN プロトコルの要件を満たさない場合があります。詳細については、セクション 3.6.1 および『DCAN モジュールのプログラミング例とデバッグ戦略』を参照してください。

特に I2C の場合は、外部プルアップ抵抗を使用して SDAA ピンと SCLA ピンを High にプルアップすることを推奨します。プルアップが強すぎる (抵抗値が小さい) と、実質的に I2C ピンが Low に駆動されなくなり、プルアップが弱すぎる (抵抗値が大きい) と、通信速度に影響を及ぼす可能性があります。この値は、消費電力と速度の間のトレードオフを考慮して選択する必要があります。プルアップ抵抗の理想的な範囲を計算するには、アプリケーション・レポート『I2C バスのプルアップ抵抗値の計算』を参照してください。

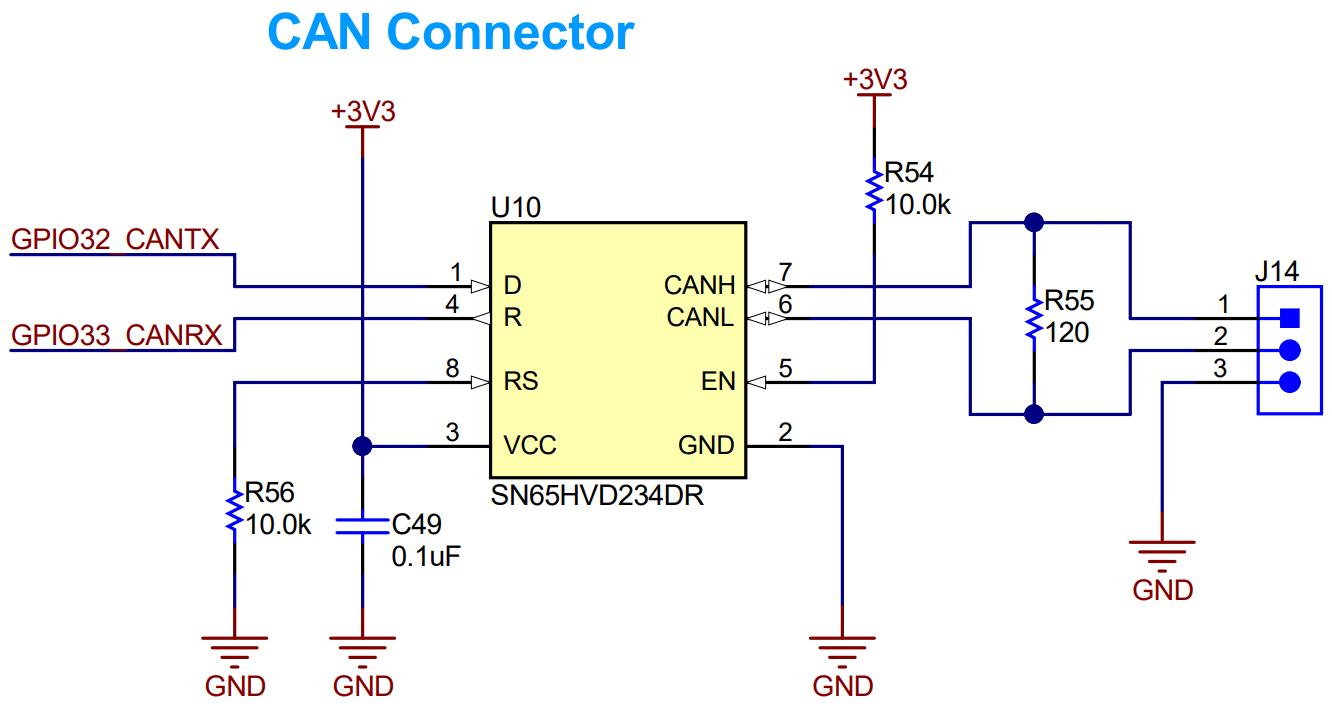

異なるプロセッサで動作する 2 つ以上のボードを接続できるインターフェイスには、SCI、CAN、LIN、FSI があります。これらのポートは多くの場合、ノイズに対処するために電気信号を変換し、他のデバイスのポートとの通信を可能にする専用のトランシーバ部品を必要とします。通信トランシーバを使用する場合、一部のトランシーバでは MCU の通信ピンにプルアップ抵抗が必要な場合があります。トランシーバのデータシートで、この要件を確認してください。

図 3-5 LAUNCHXL-F280049C の CAN トランシーバ

図 3-5 LAUNCHXL-F280049C の CAN トランシーバ 図 3-6 代表的な RS-232 トランシーバ

図 3-6 代表的な RS-232 トランシーバSCI 通信ペリフェラルは 2 線式非同期シリアル・ポートで、SCITXD (SCI 送信出力) と SCIRXD (SCI 受信入力) の 2 つの外部ピンがあります。このプロトコルは一般に UART と呼ばれ、C2000 デバイスのプロトコルは標準の NRZ フォーマットを使用します。一部のトランシーバ実装では、SCI-RX ピンにプルアップ抵抗を配置し、信号を駆動しなくても High ロジック・レベルに戻れるようにすることを推奨します。これにより、GPIO ピンが値の間でフローティングになり、エラーが発生して消費電流が増加するのとを防ぐことができます。このプルアップ抵抗の要件については、使用するトランシーバのデータシートを参照してください。使用するトランシーバの種類によっては、SCI モジュールが確定的に動作するようにするためにプルアップ抵抗が必要です。この抵抗の理想的な値はアプリケーションによって大きく異なるため、システム内でテストして選択する必要があります。プルアップ値が弱すぎる (抵抗が大きい) と、他のデバイスからのトライステート出力またはフローティング出力を抵抗でプルアップできない可能性があります。同様に、プルアップ値が強すぎる (抵抗値が小さい) と、他のデバイスから出力信号をトグルできなくなります。この値を検討する際は、10kΩ から検討するのが適切です。SCI 転送のデバッグとトラブルシューティングの詳細については、E2E の SCI FAQ スレッドを参照してください。

各種通信ペリフェラル・プロトコルの追加の参考資料については、以下のドキュメントを参照してください。