JAJU732C June 2019 – July 2022

- 概要

- Resources

- 特長

- アプリケーション

- 5

- 1System Description

- 2System Overview

- 3Circuit Description

- 4Hardware, Software, Testing Requirements, and Test Results

- 5Design Files

- 6Related Documentation

- 7Terminology

- 8About the Author

- 9Revision History

4.1.2.3 PWM Configuration

Up-down count mode is used to generate the PWMs for the primary and secondary legs of the dual active bridge. To use the high-resolution PWMs, the PRIM_LEG1_H PWM pulse is centered on the period event and the time base is configured to be up-down count. A complementary pulse with high-resolution dead time is then generated for the complementary switch. Between LEG1 and LEG2, there is a 180-degree phase shift for a full-bridge operation. This is achieved by using the feature on the PWM module to swap the xA and xB output. The PWM frequency for this application is 100 kHz. The TBPRD register is set to a value 500 in up-down count mode.

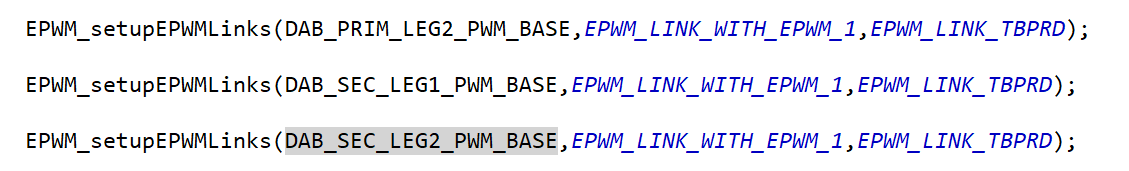

The duty cycle value is loaded in CMPA register of the EPWM base and is configured to generate 50% duty cycle. The action qualifier module outputs the required action for controlling the PWM output on a compare A event. The global link mechanism on the Type-4 PWM is used to reduce the number of cycles needed to update the registers and enables high-frequency operation. For example, the following code in the DAB_HAL_setupPWM() function links the TBPRD registers for all the PWM Legs.

Using this linkage, a single write to the PRIM_LEG1 TBPRD register writes the value to PRIM_LEG2, SEC_LEG1, and SEC_LEG2.

Figure 4-2 PWM Write