SLUAAH0 February 2022 UCC14130-Q1 , UCC14131-Q1 , UCC14140-Q1 , UCC14141-Q1 , UCC14240-Q1 , UCC14241-Q1 , UCC14340-Q1 , UCC14341-Q1 , UCC15240-Q1 , UCC15241-Q1

- Trademarks

- 1 Introduction

- 2 Three-Phase Traction Inverter

- 3 Gate Drive Bias Requirements

- 4 Single Positive Isolated Output Voltage

- 5 Dual Positive and Negative Output Voltages

- 6 Dual Positive Output Voltages

- 7 Capacitor Selection

-

8 RLIM

Current Limit Resistor

- 8.1 RLIM Functional Description

- 8.2

RLIM

Dual Output Configuration

- 8.2.1 CVEE Above Nominal Value CVDD Below Nominal Value

- 8.2.2 CVEE Below Nominal Value CVDD Above Nominal Value

- 8.2.3 Gate Driver Quiescent Current: IQ_VEE > IQ_VDD

- 8.2.4 Gate Driver Quiescent Current: IQ_VEE < IQ_VDD

- 8.2.5 CVEE Above Nominal Value CVDD Below Nominal Value: IQ_VEE > IQ_VDD

- 8.2.6 CVEE Below Nominal Value CVDD Above Nominal Value: IQ_VEE < IQ_VDD

- 8.3 RLIM Single Output Configuration

- 9 UCC14240-Q1 Excel Design Calculator Tool

- 10Thermal Considerations

- 11Enable (ENA) and Power Good (/PG)

- 12PCB Layout Considerations

- 13Reference Design Example

- 14Summary

- 15References

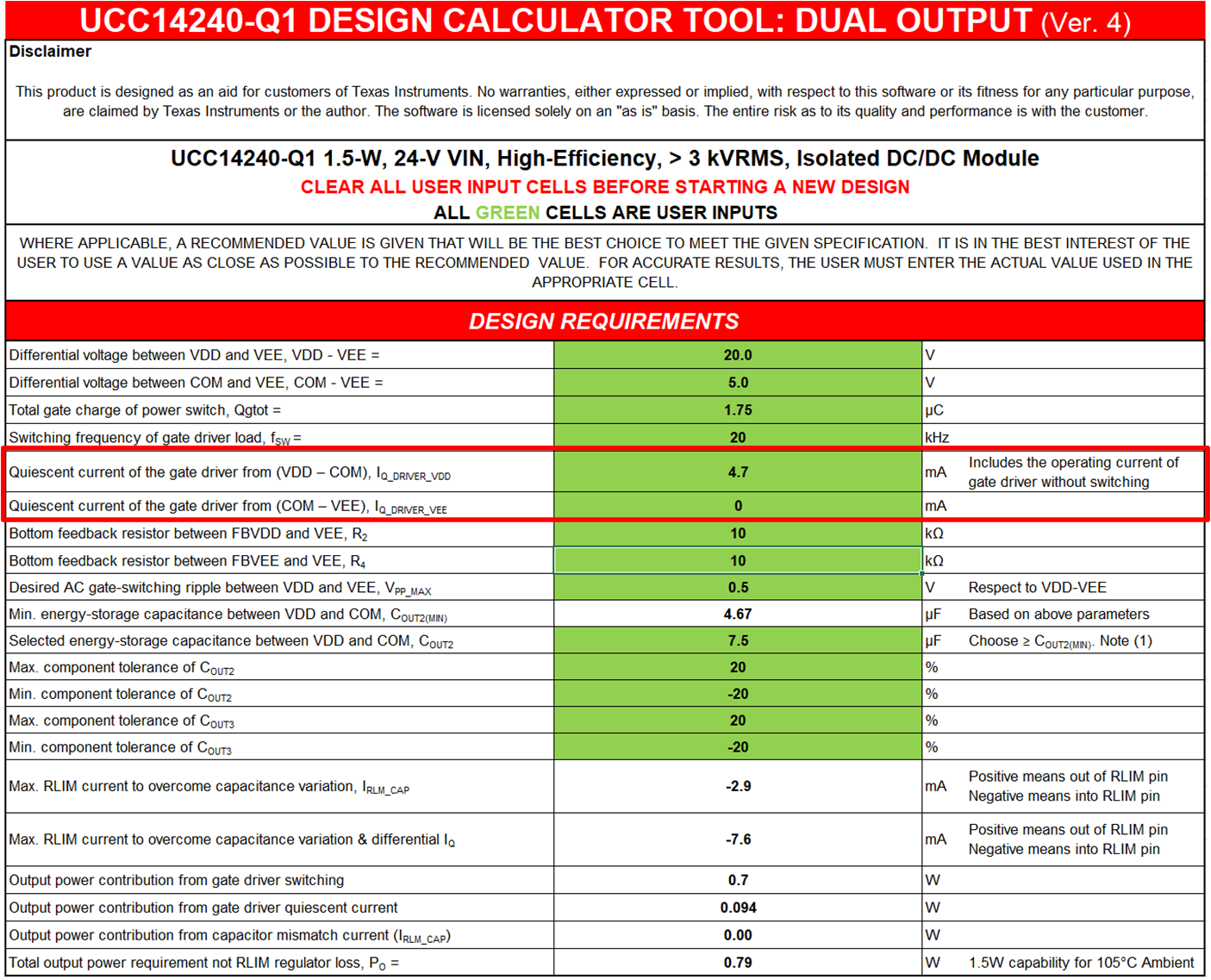

9 UCC14240-Q1 Excel Design Calculator Tool

The UCC14240-Q1 Excel Design Calculator Tool is available for download from the UCC14240-Q1 product folder on TI.com. The tool allows the user to input their known design parameters into the green boxes shown in Figure 9-1 and Figure 9-2. Based on user feedback and continuous improvement, the tool may be revised as needed, so users are encouraged to check the UCC14240-Q1 product folder for the latest version. The equations presented in this application report are used within the design calculator tool to simplify the task of quickly setting up the UCC14240-Q1.

The requested parameters are intuitive and each of the charge mismatch cases introduced in Section 8.2 are calculated to help select the proper RLIM value covering all cases. The quiescent current, IQ values will need to be obtained from the gate driver data sheet. Considering the worst-case mismatch, the UCC21736-Q1 10-A Source and Sink Reinforced Isolated Single Channel Gate Driver for SiC/IGBT with Active Protection and High-CMTI data sheet gives a maximum value of IQ_VDD=4.7 mA (OUT(L)) and a minimum value of IQ_VEE=830 µA (OUT(H)). Sometimes IQ_VEE may not be specified in the gate driver data sheet. In such cases, only the difference between IQ_VDD and IQ_VEE is used to calculate RLIM and IQ_VEE=0 A can be used as a worst-case.

Figure 9-1 UCC14240-Q1 Design Tool: Design Inputs (Green)

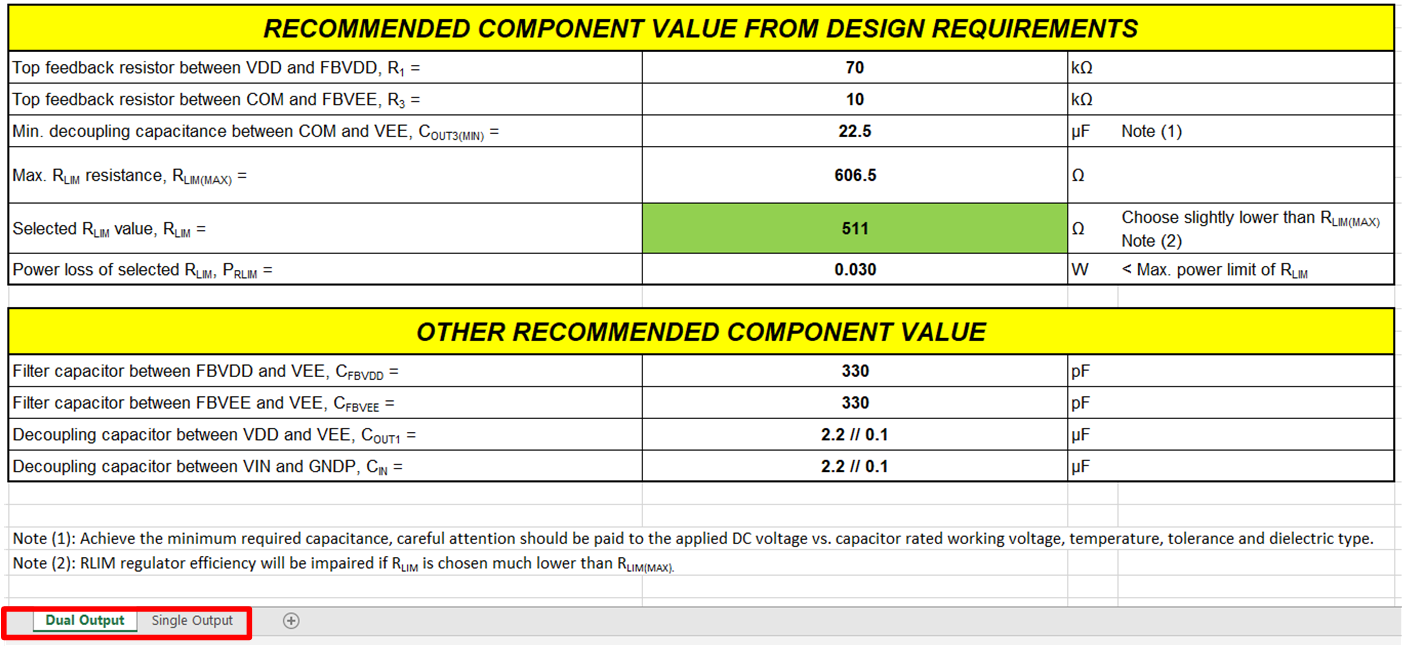

As highlighted in Figure 9-2, there are two selectable tabs available at the bottom of the design tool, allowing the user to configure the UCC14240-Q1 for either dual or single output, as shown in Figure 5-1 and Figure 4-1.

Figure 9-2 UCC14240-Q1 Design Tool: Dual vs. Single Output