SPRACN9E september 2022 – may 2023 AM67 , AM67A , AM68 , AM68A , AM69 , AM69A , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4AEN-Q1 , TDA4VEN-Q1 , TDA4VM , TDA4VM-Q1

- 1

- Jacinto 7 LPDDR4 Board Design and Layout Guidelines

- Trademarks

- 1Overview

-

2LPDDR4 Board Design and Layout Guidance

- 2.1 LPDDR4 Introduction

- 2.2 LPDDR4 Device Implementations Supported

- 2.3 LPDDR4 Interface Schematics

- 2.4 Compatible JEDEC LPDDR4 Devices

- 2.5 Placement

- 2.6 LPDDR4 Keepout Region

- 2.7 Net Classes

- 2.8 LPDDR4 Signal Termination

- 2.9 LPDDR4 VREF Routing

- 2.10 LPDDR4 VTT

- 2.11 CK and ADDR_CTRL Topologies

- 2.12 Data Group Topologies

- 2.13 CK and ADDR_CTRL Routing Specification

- 2.14 Data Group Routing Specification

- 2.15 Channel, Byte, and Bit Swapping

- 3LPDDR4 Board Design Simulations

- 4Revision History

3.6.3 Model Verification

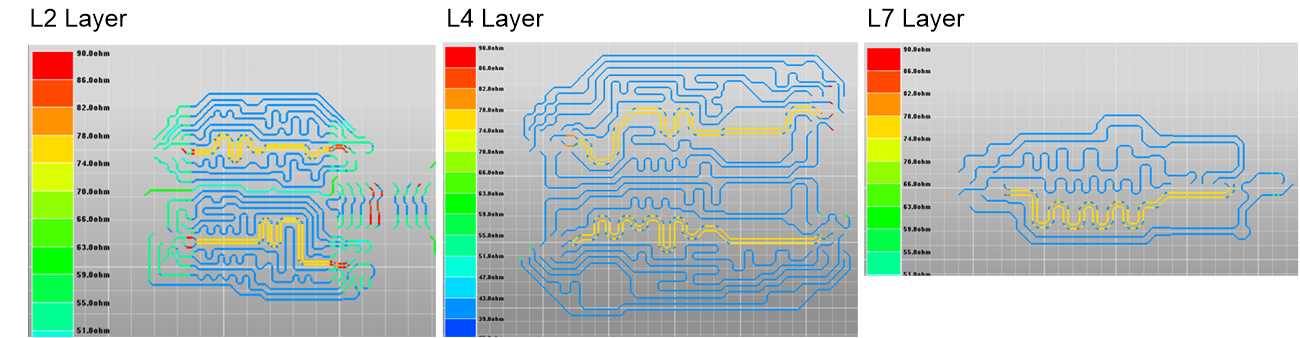

Before simulating, it is recommended to verify the models. One verification method described is the impedance plot (or impedance scan). The Impedance scans for a 10 layer design are provided.

Figure 3-10 Example LPDDR4 Trace Impedance Scan

Figure 3-10 Example LPDDR4 Trace Impedance ScanTable 3-8 Example LPDDR4 Trace Impedance Summary for Data

| Layer | DDR Bus | DQ SE Impedance (Ω) | DQS/CLK Difference Impedance (Ω) |

|---|---|---|---|

| L2 | B1 and B3 | 40.9 | 77.7 |

| L2 | CA | 51.7 | 101.4 |

| L4 | B0 and B2 | 41.1 | 77.7 |

| L7 | CA | 41.1 | 77.7 |

For CK and CA signals, the goal is to have the branch segment equal to two times the impedance of the feed trace. Note its common for the PCB to limit the achievable impedances. Simulations will show you if the compromises are acceptable.

Table 3-9 Example LPDDR4 Trace Impedance Summary for CA

| Board | CA Feed Impedance (Ω) | CA Branch Impedance (Ω) | CA Branch Target (Ω) | Impedance Mismatch (Ω) |

|---|---|---|---|---|

| Initial Design | 49.1 | 59.6 | 98 (49x2) | 38.6 |

| Final Design | 41.1 | 51.7 | 82 (41x2) | 30.5 |

The simulation results show the improvement made by closer matching the impedances to their targets.

Table 3-10 Example LPDDR4 Simulation Results From Improved Trace Impedance

| Board | Total Eye Width Margin (ps) | Total Eye Height Margin (ps) | Min Ringback Margin H (mV) | Min Ringback Margin L (mV) |

|---|---|---|---|---|

| Initial Design | 58.00 | 14.00 | 69.59 | 18.18 |

| Final Design | 124.68 | 48.08 | 89.43 | 25.49 |