SPRAD61A March 2023 – November 2023 AM2732 , AM2732 , AM2732-Q1 , AM2732-Q1

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Power

- 3 Clocking

- 4 Resets

- 5 Bootstrapping

- 6 JTAG Emulators and Trace

- 7 Multiplexed Peripherals

- 8 Digital Peripherals

- 9 Layer Stackup

- 10Vias

- 11BGA Power Fan-Out and Decoupling Placement

- 12References

- 13Revision History

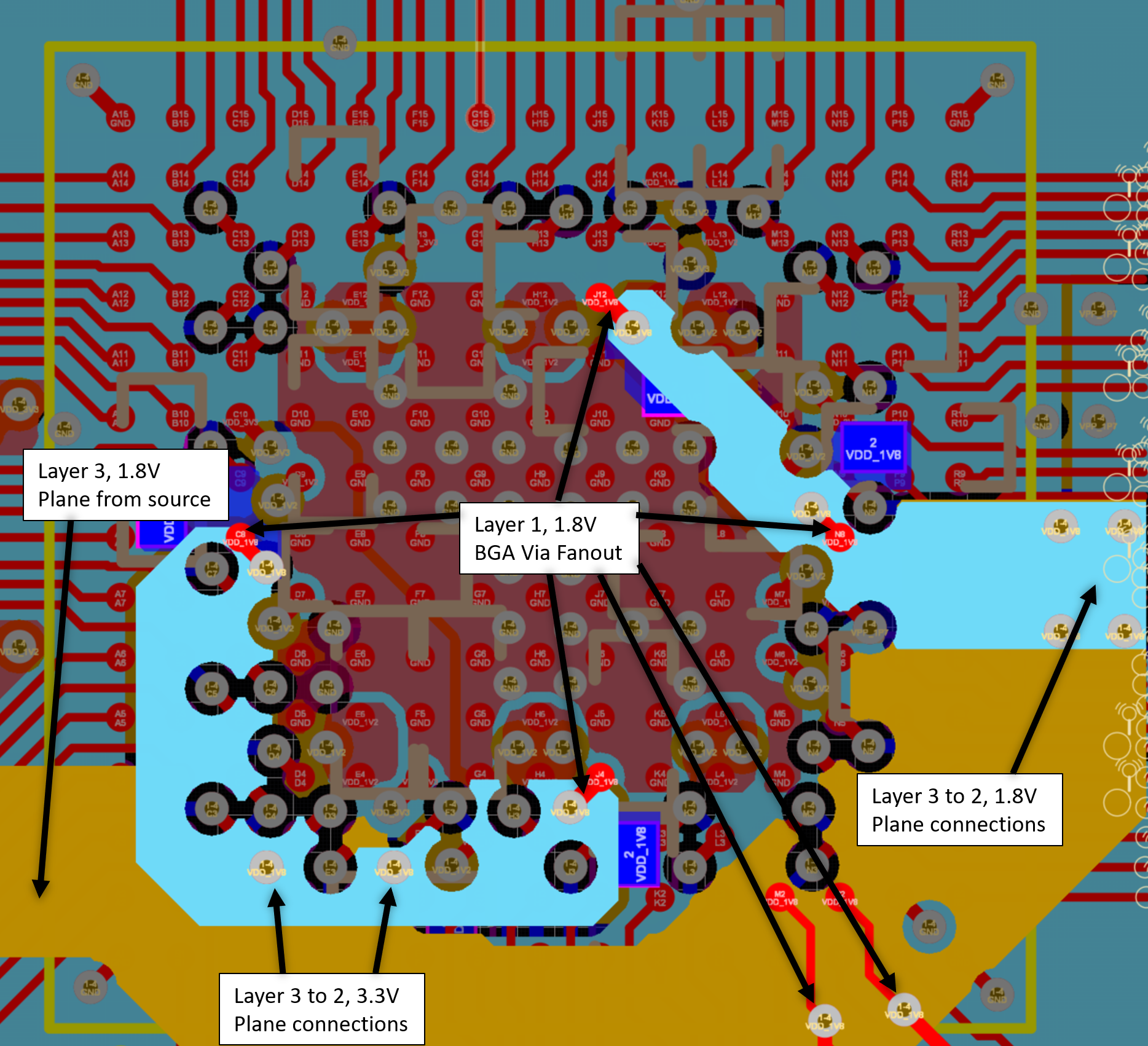

11.4.1.3 1.8V Digital and Analog Layout - NZN Four Layer Example

On the AM273 NZN Four Layer Example, the 1.8 V plane is shown routing to and underneath the AM273 device primarily on layer 3. Due to routing limitations caused by a four layer PCB, underneath the AM273 device the 1.8 V plane is split between layers 2 and 3.

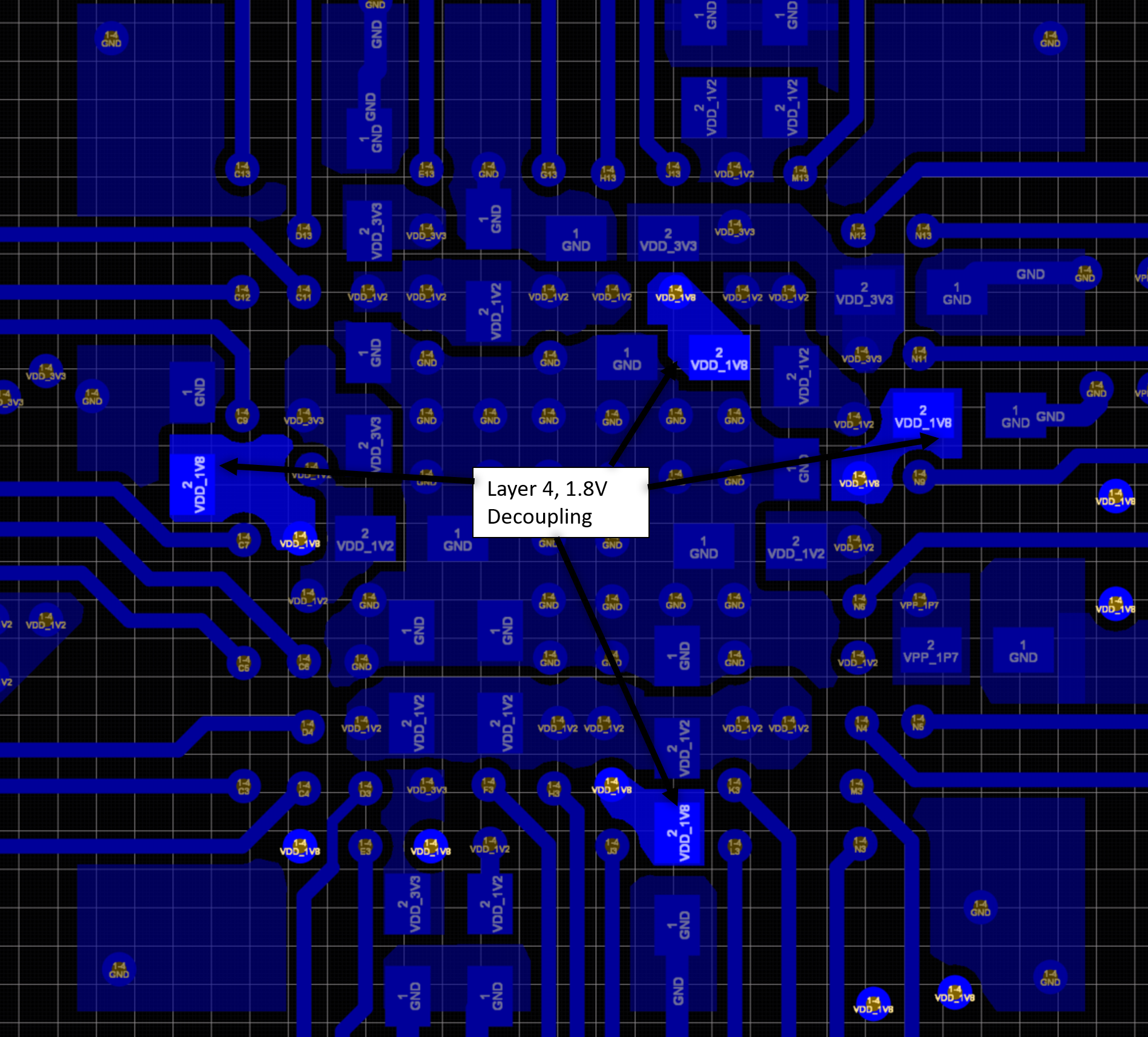

The 1.8V planes on layer 2 split up an otherwise solid ground pour on layer 2. The placement of these cutouts was chosen to minimize the impact to the signal return paths for as many GPIO pins as possible. Vias connect the plane on layers 2 and 3 to the BGA ball pads on the top layer and the decoupling capacitors on the bottom layer.

Figure 11-26 NZN 4 Layer Example Excerpt – 1.8 V Power Via Fan-Out and Plane Routing Layer 3

Figure 11-26 NZN 4 Layer Example Excerpt – 1.8 V Power Via Fan-Out and Plane Routing Layer 3 Figure 11-27 NZN 4 Layer Example Excerpt – 1.8 V Power Decoupling on Layer 4

Figure 11-27 NZN 4 Layer Example Excerpt – 1.8 V Power Decoupling on Layer 4