SPRAD61A March 2023 – November 2023 AM2732 , AM2732 , AM2732-Q1 , AM2732-Q1

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Power

- 3 Clocking

- 4 Resets

- 5 Bootstrapping

- 6 JTAG Emulators and Trace

- 7 Multiplexed Peripherals

- 8 Digital Peripherals

- 9 Layer Stackup

- 10Vias

- 11BGA Power Fan-Out and Decoupling Placement

- 12References

- 13Revision History

6 JTAG Emulators and Trace

The AM273x MCU supports multiple different classes of JTAG emulators with or without additional ARM Trace capture capabilities.

For out of box convenience the TMDS273GPEVM implements an onboard XDS110 emulator with JTAG and auxiliary UART-USB bridge using a TI TM4C MCU. However, for actual custom systems, a simpler JTAG/Trace debug header should be implemented. This allows for external JTAG and Trace pods to be attached to the system as needed during development. The header can then be removed entirely or depopulated for full production of the system to save cost.

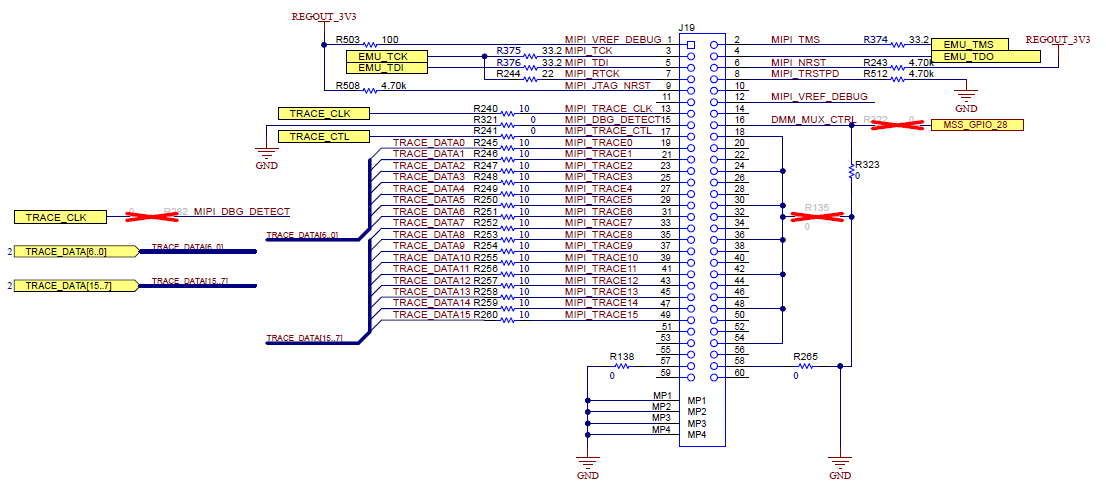

One popular JTAG and Trace implementation is the MIPI industry standard MIPI-60 shown in [5]. This is based on the Samtec QSH-030-01-L-D-A. This implementation is compatible with TI XDS560v2 JTAG/Trace pods as well as other third-party JTAG/Trace pods. Additional TI JTAG debugger connections can be found in [6].

Figure 6-1 Example MIPI-60 JTAG and 16-Bit Trace Implementation

Figure 6-1 Example MIPI-60 JTAG and 16-Bit Trace Implementation Additional, non-TI JTAG debug and Trace systems are still being tested. Further guidance is planned in future revisions of this document.