JAJU732C June 2019 – July 2022

- 概要

- Resources

- 特長

- アプリケーション

- 5

- 1System Description

- 2System Overview

- 3Circuit Description

- 4Hardware, Software, Testing Requirements, and Test Results

- 5Design Files

- 6Related Documentation

- 7Terminology

- 8About the Author

- 9Revision History

4.1.2.4 High-Resolution Phase Shift Configuration

High-resolution features used:

- High-Resolution Phase Shift

- High-Resolution Dead Band

- High-Resolution Duty → Not available, CTMODEB is set to 1

- High-Resolution Period → Not available, CTMODEB is set to 1

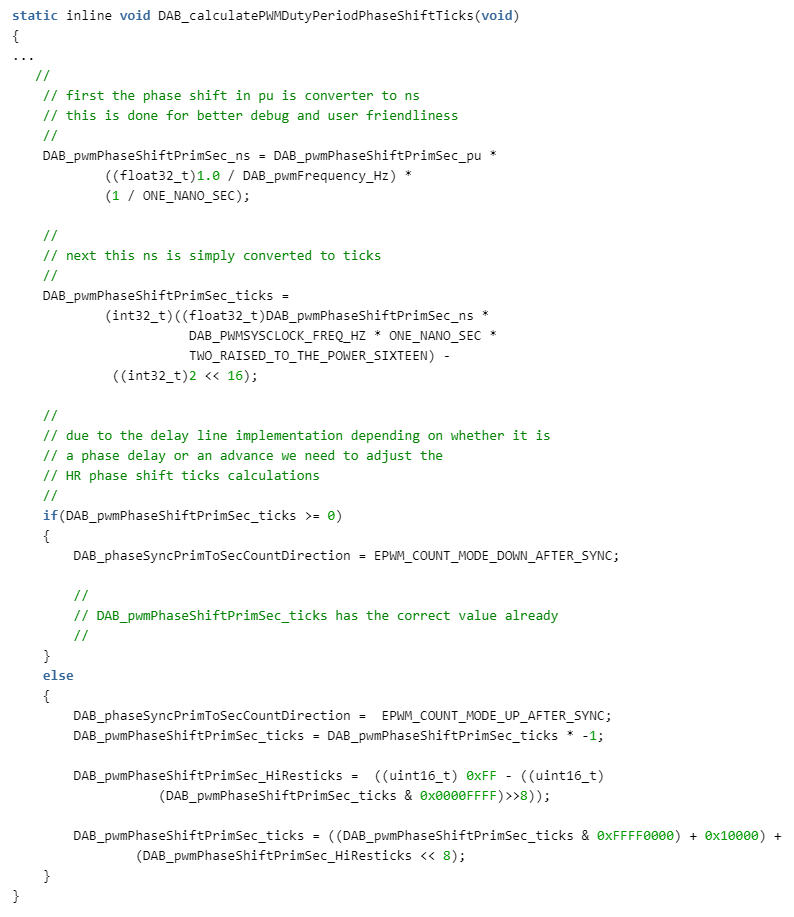

The PWM pulses of the secondary side are phase-shifted with respect to the PWM pulses of the primary. Controlling the phase shift enables transfer of power between the primary and secondary and vice versa. The maximum power transferred is very sensitive to the value of phase shift in a Dual Active Bridge. A small series inductor can lead to maximum power transfer at a small value of phase shift. Since the range over which the phase shift is going to be varied is small, and accurate control would require fine increment and decrement steps of phase. The phase control is implemented using Hi-Res (high resolution) feature of F28004x. The function DAB_calculatePWMDutyPeriodPhaseShiftTicks() inside ISR1 calculates the required the required high resolution phase control for both voltage and current mode control. This helps in handling sudden load changes smoothly without producing huge overshoots/transients in the current waveforms.

Figure 4-3 PWM Function 1

Figure 4-4 PWM Function 2

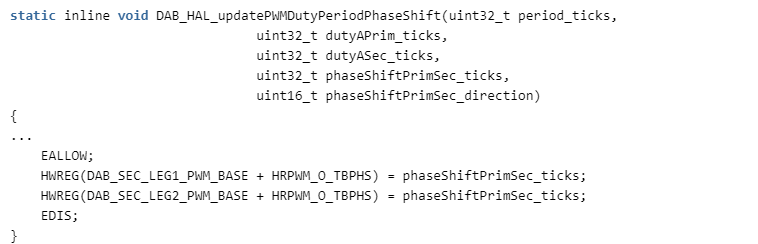

The variable 'DAB_phaseSyncPrimToSecCountDirection' is updated to control the forward mode or reverse mode of power flow.

Figure 4-5 PWM Config