SBAA532A February 2022 – March 2024 ADS1119 , ADS1120 , ADS1120-Q1 , ADS112C04 , ADS112U04 , ADS1130 , ADS1131 , ADS114S06 , ADS114S06B , ADS114S08 , ADS114S08B , ADS1158 , ADS1219 , ADS1220 , ADS122C04 , ADS122U04 , ADS1230 , ADS1231 , ADS1232 , ADS1234 , ADS1235 , ADS1235-Q1 , ADS124S06 , ADS124S08 , ADS1250 , ADS1251 , ADS1252 , ADS1253 , ADS1254 , ADS1255 , ADS1256 , ADS1257 , ADS1258 , ADS1258-EP , ADS1259 , ADS1259-Q1 , ADS125H01 , ADS125H02 , ADS1260 , ADS1260-Q1 , ADS1261 , ADS1261-Q1 , ADS1262 , ADS1263 , ADS127L01 , ADS130E08 , ADS131A02 , ADS131A04 , ADS131E04 , ADS131E06 , ADS131E08 , ADS131E08S , ADS131M02 , ADS131M03 , ADS131M04 , ADS131M06 , ADS131M08

- 1

- Abstract

- Trademarks

- 1Bridge Overview

- 2Bridge Construction

- 3Bridge Connections

- 4Electrical Characteristics of Bridge Measurements

- 5Signal Chain Design Considerations

-

6Bridge Measurement Circuits

- 6.1 Four-Wire Resistive Bridge Measurement with a Ratiometric Reference and a Unipolar, Low-Voltage (≤5 V) Excitation Source

- 6.2 Six-Wire Resistive Bridge Measurement With a Ratiometric Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source

- 6.3 Four-Wire Resistive Bridge Measurement With a Pseudo-Ratiometric Reference and a Unipolar, High-Voltage (> 5 V) Excitation Source

- 6.4 Four-Wire Resistive Bridge Measurement with a Pseudo-Ratiometric Reference and Asymmetric, High-Voltage (> 5 V) Excitation Source

- 6.5 Four-Wire Resistive Bridge Measurement With a Ratiometric Reference and Current Excitation

- 6.6 Measuring Multiple Four-Wire Resistive Bridges in Series with a Pseudo-Ratiometric Reference and a Unipolar, Low-Voltage (≤5V) Excitation Source

- 6.7 Measuring Multiple Four-Wire Resistive Bridges in Parallel Using a Single-Channel ADC With a Ratiometric Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source

- 6.8 Measuring Multiple Four-Wire Resistive Bridges in Parallel Using a Multichannel ADC With a Ratiometric Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source

- 7Summary

- 8Revision History

6.6.4 Design Notes

The unipolar excitation voltage, VEXCITATION, is used as the ADC supply voltage (AVDD) as well as the ADC reference voltage, VREF. Small variations in the bridge resistance due to tension or compression cause the differential output voltage for each bridge to change. The bridge output voltage is reduced compared to a single bridge measurement because VEXCITATION is divided between Bridge A and Bridge B. The PGA integrated into the ADC gains up the low-level bridge output signal to reduce system noise and utilize more of the ADC full-scale range (FSR). The ADC samples and converts this amplified voltage against VREF. This measurement is not ratiometric because the output voltage of Bridge A can change depending on the properties of Bridge B (and vice versa). This dependence occurs even in the absence of a change in the applied load, resulting in a pseudo-ratiometric reference configuration. This challenge can be removed by using a dedicated set of reference inputs per bridge, assuming the ADC has multiple differential reference inputs.

Measuring multiple four-wire resistive bridges in series using a pseudo-ratiometric reference and a unipolar, low-voltage (≤ 5 V) supply requires:

- Multiple differential analog inputs (AINPx and AINNx) or external multiplexer

- External reference input (dedicated pin or use analog supply)

- Low-noise amplifier

When implementing a circuit with multiple bridges in series, it is important to use sensors with similar parameters (should be the same for each bridge) as mentioned in Table 6-18. Following this guideline simplifies how the common-mode voltage for each bridge is determined. Additionally, using bridges with different nominal resistances can introduce gain errors as well as make it more challenging to determine the load weight. This latter challenge can be removed by using a dedicated set of reference inputs per bridge, assuming the ADC has multiple differential reference inputs.

To begin a design, start by using the equations in Table 6-19 to calculate the bridge output common-mode voltage, VCM(Bridge_A) and VCM(Bridge_B), under a no-load condition (R1 = R2 = R3 = R4). For example, if RBRIDGE = 1 kΩ and VEXCITATION = 5 V, Equation 65 and Equation 66 yield the following results:

Figure 6-12 shows the voltage level at each input of the ADC multiplexer and how each will be applied to the same amplifier.

Figure 6-12 Common-Mode Voltage for Two Bridges in a Series Configuration

Figure 6-12 Common-Mode Voltage for Two Bridges in a Series ConfigurationUnlike the previous examples where one of the system parameters was a specific ADC amplifier common-mode voltage target, a series combination of bridges requires identifying the ADC amplifier common-mode voltage range, VCM(ADC)_RANGE. This range helps accommodate a potentially wide variance between VCM(Bridge_A) and VCM(Bridge_B), which is the case in Figure 6-12. As described in Section 6.3.4, many ADCs used for bridge measurement applications have support collateral that can help identify the ADC amplifier common-mode range for a particular set of input conditions.

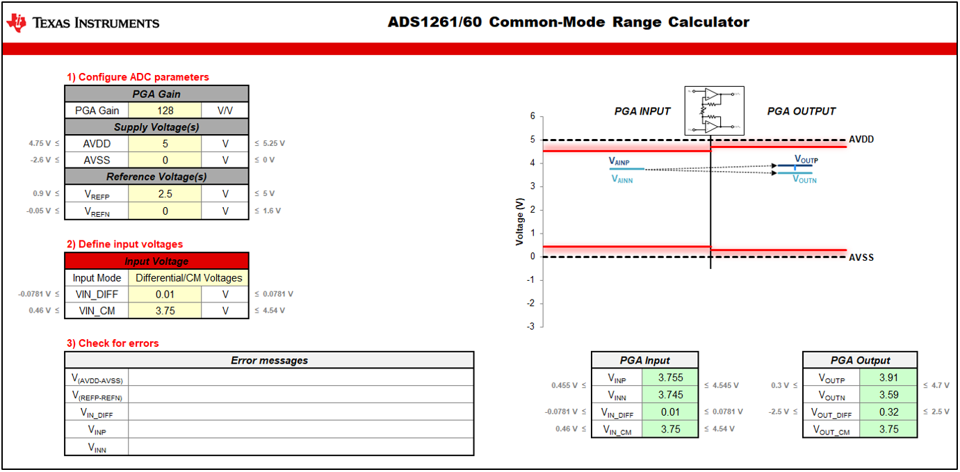

Figure 6-13 shows an example of how the Common-Mode Range Calculator from the ADS1261 Excel Calculator can be used to determine if VCM(Bridge_A) and VCM(Bridge_B) are within the input range of the amplifier integrated into the ADS1261.

Figure 6-13 Verifying System Requirements Using the ADS1261 VCM Calculator Tool

Figure 6-13 Verifying System Requirements Using the ADS1261 VCM Calculator ToolIn Figure 6-13, VIN_CM = 3.75 V to check if the ADC amplifier can accept VCM(Bridge_A). The tool shows no errors for an input signal with this common-mode voltage, indicating that this is a valid input condition when gain = 128, AVDD = 5 V, and VIN_DIFF = 10 mV (though not shown, VIN_CM = 1.25 V is also a valid input condition). Moreover, the tool shows that for these specific settings, VCM(ADC)_RANGE extends from 0.45 V to 4.54 V, indicating that the ADC amplifier can accept both VCM(Bridge_A) and VCM(Bridge_B).

Note that VCM(ADC)_RANGE depends on the PGA gain in this example. Therefore, the PGA gain for each bridge must be selected in conjunction with confirming that VCM(Bridge_A) and VCM(Bridge_B) are within VCM(ADC)_RANGE. The PGA gain should be the largest allowable value that is still less than the ADC FSR. In some cases it is not possible to choose an amplifier gain that uses the entire ADC FSR. While this is often an acceptable tradeoff between resolution and ease-of-use, care should be taken to ensure that all system requirements are still met when the ADC FSR cannot be maximized.

Next, identify the maximum differential output voltage of each bridge, VOUT(Bridge Max), using the equation from Table 6-19 and parameters from Table 6-18. This value provides the maximum output voltage possible from the bridge under normal operating conditions and corresponds to the maximum load that can be applied to the bridge, Load(Bridge Max). If the system does not use the entire bridge output range, VOUT(System Max) defines the maximum differential output signal that is applied to a specific system and Load(System Max) is the corresponding maximum load. For example, if VOUT(Bridge Max) corresponds to Load(Bridge Max) = 5 kg, but the system specifications only require that Load(System Max) = 2.5 kg, then VOUT(System Max) is given by Equation 67:

Note that if Load(System Max) = Load(Bridge Max), then VOUT(System Max) = VOUT(Bridge Max).

Finally, follow the instructions in Section 5.5 if calibration is required. Note that each bridge in Figure 6-11 must be calibrated separately, requiring the host processor to calculate and store multiple sets of calibration coefficients.