SLAAED9 November 2023 TAA5412-Q1 , TAC5311-Q1 , TAC5312-Q1 , TAC5412-Q1

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Diagnostic Monitoring Architecture

- 3 Monitored Faults

- 4 Enabling Diagnostics and Programming Thresholds

- 5 Fault Diagnostic Setup Procedure

-

6 Fault Reporting

- 6.1

Live Registers

- 6.1.1 CHx_LIVE Register (page = 0x01, address = 0x3D) [Reset = 0b]

- 6.1.2 CH1_LIVE Register (page = 0x01, address = 0x3E) [Reset = 0h]

- 6.1.3 INT_LIVE0 Register (page = 0x01, address = 0x3C) [Reset = 00]

- 6.1.4 INT_LIVE1 Register (page = 0x00, address = 0x42) [reset = 0x00]

- 6.1.5 INT_LIVE2 Register (page = 0x00, address = 0x43) [reset = 0x00]

- 6.2 Latched Registers

- 6.3 Fault Filtering and Response Time

- 6.1

Live Registers

- 7 Responding to a Fault

- 8 Using PurePath Console

- 9 Diagnostic Monitoring Registers

- 10Summary

- 11References

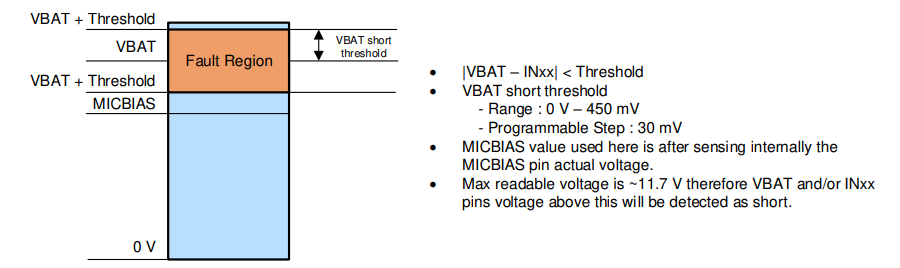

3.1.6 Inputs Shorted to VBAT

This fault triggers when the absolute value of the difference between the voltage applied to the VBAT pin and the input pin is less than the programmed threshold. The programmable range is 0 V to 450 mV in steps of 30 mV.

Figure 3-6 Input Short to VBAT Conditions

When VBAT > MICBIAS

Figure 3-6 Input Short to VBAT Conditions

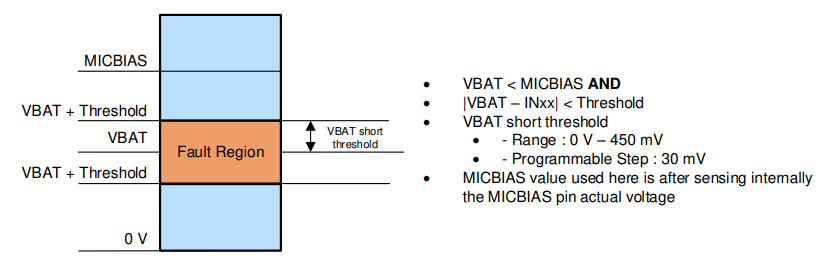

When VBAT > MICBIASIn most automotive applications, the battery voltage is not expected to dip below MICBIAS, which has a maximum programmable value of 10 V. As long as VBAT is greater than MICBIAS, then a short to VBAT fault also produces an overvoltage fault. In rare cases, VBAT can be less than MICBIAS. This scenario can occur if the battery is heavily loaded or a voltage divider is used prior to VBAT_IN. In these cases, the fault can falsely trigger based on the signal level on the INxx pin. To avoid or minimize false detections, using the debounce and averaging features described in Section 6.3 are recommended. The debounce for this specific condition can be programmed independently from the other faults, or detection of this fault can be disabled altogether.

Figure 3-7 Input Short to VBAT Conditions

When VBAT < MICBIAS

Figure 3-7 Input Short to VBAT Conditions

When VBAT < MICBIAS