SPRUJ12F August 2021 – January 2024 AM2431 , AM2432 , AM2434

- 1

- Abstract

- Trademarks

- 1Preface: Read This First

- 2Kit Overview

- 3Board Setup

-

4Hardware Description

- 4.1 Functional Block Diagram

- 4.2 BoosterPack Headers

- 4.3 GPIO Mapping

- 4.4 Reset

- 4.5 Clock

- 4.6 Memory Interface

- 4.7 Ethernet Interface

- 4.8 USB 2.0 Interface

- 4.9 I2C Interface

- 4.10 Industrial Application LEDs

- 4.11 UART Interface

- 4.12 eQEP Interface

- 4.13 CAN Interface

- 4.14 FSI Interface

- 4.15 JTAG Emulation

- 4.16 Test Automation Interface

- 4.17 SPI Interface

- 5References

- A E3 Design Changes

- B Revision A Design Changes

- Revision History

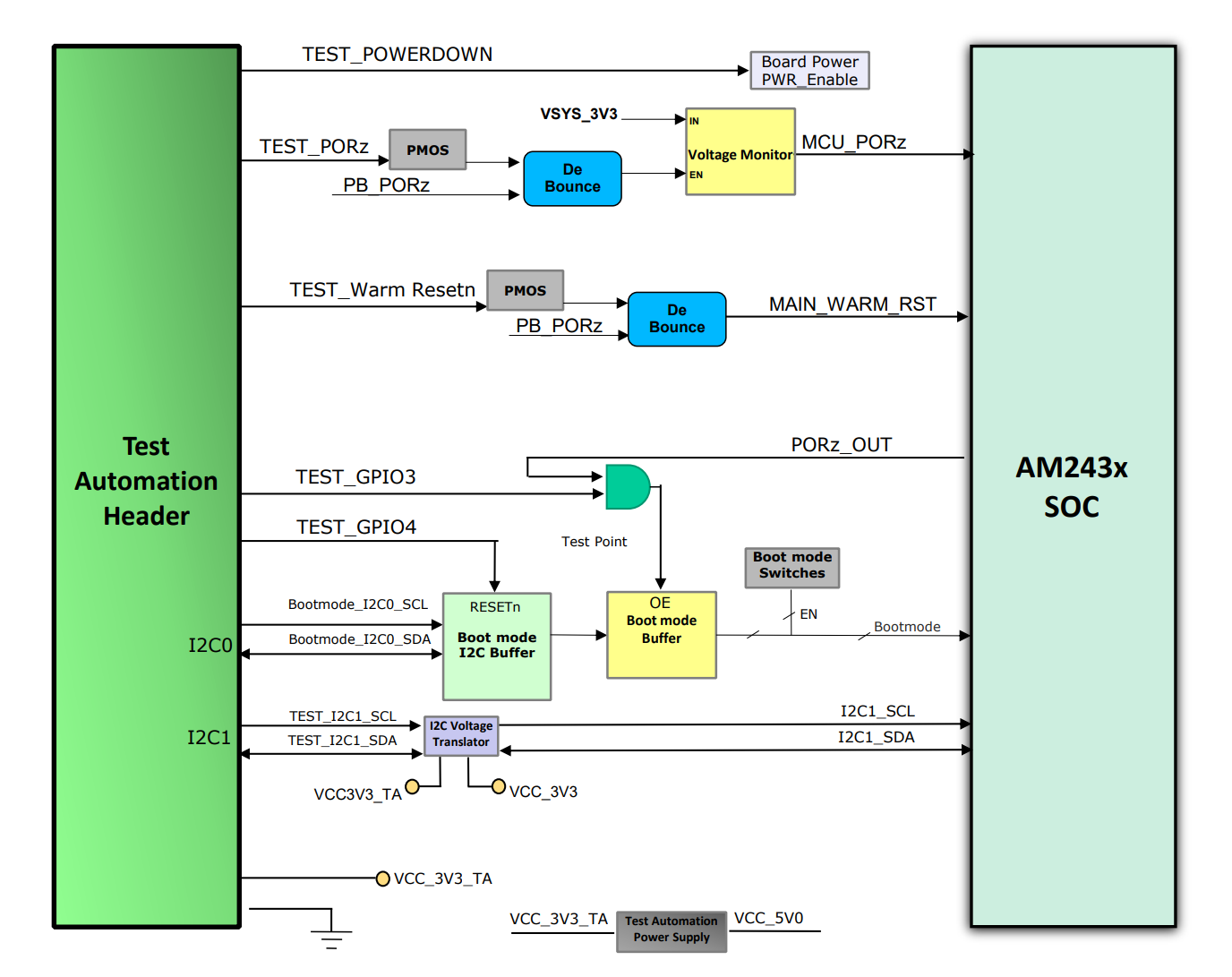

4.16 Test Automation Interface

The LaunchPad supports a 40-pin test automation header (687140183622 from Wurth) that allows an external controller to manipulate some basic operations like power down, power on reset (POR), warm reset, boot mode control and other functions.

Figure 4-28 Test Automation Header

Figure 4-28 Test Automation Header| Signal | Signal Type | Function |

|---|---|---|

| POWER_DOWN | GPIO | Instructs the LaunchPad to power down all circuits |

| PORZn | GPIO | Creates a PORz into the AM243x |

| WARM_RESETn | GPIO | Creates a RESETz into the AM243x |

| GPIO3 | GPIO | Disables the boot mode buffer |

| GPIO4 | GPIO | Resets the bootmode IO expander |

| Bootmode_I2C | I2C | communicates with bootmode I2C buffer |

| I2C1 | I2C | For internal testing |

The test automation circuit has voltage translation circuits so that the controller is isolated from the IO voltages used by the AM243x. Boot mode for the AM243x can be controlled by either the DIP switch or the test automation header through the I2C IO expander.

A boot mode buffer (SN74AVC8T245RHL) is used to isolate the boot mode controls that are driven through either the DIP switch or the I2C IO expander. The test automation circuit is powered by an always on supply that is generated from a dedicated regulator (TPS7A0533PDBVT).

The test automation header supports two I2C interfaces. Bootmode_I2C connects to the boot mode buffer to control the bootmode of the AM243x while the other I2C interface is connected to the I2C1 port of the AM243x.

| Pin # | IO Direction | Signal | Description |

|---|---|---|---|

| 1 | Power | VCC3V3_TA | Power for test automation header |

| 2 | Power | VCC3V3_TA | |

| 3 | Power | VCC3V3_TA | |

| 4 | N/A | Reserved | |

| 5 | N/A | Reserved | |

| 6 | N/A | Reserved | |

| 7 | Ground | DGND | |

| 8 | N/A | Reserved | |

| 9 | N/A | Reserved | |

| 10 | N/A | Reserved | |

| 11 | N/A | Reserved | |

| 12 | N/A | Reserved | |

| 13 | N/A | Reserved | |

| 14 | N/A | Reserved | |

| 15 | N/A | Reserved | |

| 16 | Ground | DGND | |

| 17 | N/A | Reserved | |

| 18 | N/A | Reserved | |

| 19 | N/A | Reserved | |

| 20 | N/A | Reserved | |

| 21 | N/A | Reserved | |

| 22 | N/A | Reserved | |

| 23 | N/A | Reserved | |

| 24 | N/A | Reserved | |

| 25 | Ground | DGND | |

| 26 | Output | TEST_POWERDOWN | Used to power down the board |

| 27 | Output | TEST_PORZn | Used to reset the SoC PORz |

| 28 | Output | TEST_WARMRESETn | Used to reset the SoC Warm Reset |

| 29 | N/A | Reserved | |

| 30 | Output | TA_SOC_INTn | Interrupt to SoC |

| 31 | Bidirectional | TEST_GPIO2 | |

| 32 | Output | TEST_GPIO3 | Used to disable the BOOTMODE buffer |

| 33 | Outpu | TEST_GPIO4 | Used to Reset the BOOTMODE IO Expander |

| 34 | Ground | DGND | |

| 35 | N/A | Reserved | |

| 36 | Bidirectional | SOC_I2C1_TA_SCL | Clock signal for SoC I2C |

| 37 | Bidirectional | BOOTMODE_I2C_SCL | Clock signal for I2C IO expander for boot mode |

| 38 | Bidirectional | SOC_I2C1_TA_SDA | Data signal for SoC I2C |

| 39 | Bidirectional | BOOTMODE_I2C_SDA | Data signal for I2C IO expander for boot mode |

| 40 | Ground | DGND | |

| 41 | Ground | DGND | |

| 42 | Ground | DGND |