Packaging information

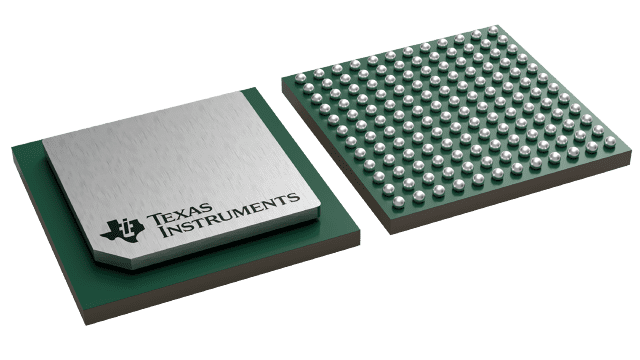

| Package | Pins FCCSP (AAV) | 144 |

| Operating temperature range (°C) -40 to 85 |

| Package qty | Carrier 168 | JEDEC TRAY (5+1) |

Features for the DAC38RF86

- 14-Bit Resolution

- Maximum DAC Sample Rate:

- 9.0 GSPS (DAC38RF86, DAC38RF96)

- 6.2 GSPS (DAC38RF87, DAC38RF97)

- Key

Specifications:

- RF Full-Scale Output Power at 2.1 GHz:0 dBm

- Spectral Performance, DAC38RF87/97

-

fDAC = 5898.24 MSPS, fOUT = 2.14 GHz

- WCDMA ACLR: 73 dBc

- WCDMA alt-ACLR: 77 dBc

-

fDAC = 5898.24 MSPS, fOUT = 2.14 GHz

- Spectral Performance, DAC38RF86/96

- fDAC = 8847.36 MSPS,

fOUT = 3.7 GHz

- 20 MHz LTE ACLR: 66 dBc

- fDAC = 9 GSPS,

fOUT = 1.8 GHz, –6 dBFS

- IMD3 = 70 dBc (10-MHz tone spacing)

- fDAC = 8847.36 MSPS,

fOUT = 3.7 GHz

- Dual-Band

Digital Up-converter per DAC

- 6, 8, 10, 12, 16, 18, 20 or 24x Interpolation

- 4 Independent NCOs With 48-Bit Resolution

- JESD204B Interface, Subclass

1

- Support for Multichip Synchronization

- Maximum Lane Rate: 12.5 Gbps

- Single-Ended Output With Integrated Balun Covering 700 MHz to 3800 MHz

- Internal PLL and VCO

- DAC38RF86/96: fC(VCO) = 8.85 GHz

- DAC38RF87/97: fC(VCO) = 5.90 GHz

- Power Dissipation: 1.4 to 2.2 W/ch

- Power Supplies: –1.8 V, 1 V, 1.8 V

- Package: 10 x 10 mm BGA, 0.8 mm Pitch, 144-Balls

Description for the DAC38RF86

The DAC38RF86/96 is a family of high-performance, dual-channel, 14-bit, 9-GSPS, RF-sampling digital-to-analog converters (DACs) that are capable of synthesizing wideband signals from 0 to 4.5 GHz. The DAC38RF87/97 is also a family of high-performance, dual-channel, 14-bit, 6-GSPS, RF-sampling digital-to-analog converters (DACs) that are capable of synthesizing wideband signals from 0 to 3 GHz. A high dynamic range allows the DAC38RFxx family to generate signals for a wide range of applications including 3G/4G signals for wireless base-stations and radar.

The devices feature a low-power JESD204B Interface with up to 8 lanes with a maximum bit rate of 12.5 Gbps allowing an input data rate of 1.25 GSPS complex per channel. The DAC38RFxx provides two digital up-converters per channel, with multiple options for interpolation rates. A digital quadrature modulator with independent, frequency flexible NCOs are available to support multi-band operation. A GSM compliant low phase noise PLL/VCO is integrated to simplify the DAC sampling clock generation by allowing the use of a lower frequency reference clock