Packaging information

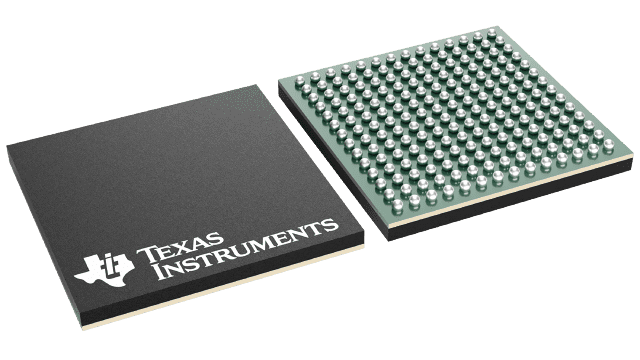

| Package | Pins NFBGA (ZAY) | 196 |

| Operating temperature range (°C) -40 to 85 |

| Package qty | Carrier 160 | JEDEC TRAY (5+1) |

Features for the ADS54T02

- Dual Channel

- 12-Bit Resolution

- Maximum Clock Rate: 750 Msps

- Low Swing Fullscale Input: 1.0 Vpp

- Analog Input Buffer with High Impedance Input

- Input Bandwidth (3dB): >1.2GHz

- Data Output Interface: DDR LVDS

- 196-Pin BGA Package (12×12mm)

- Power Dissipation: 1050mW/ch

- Performance at fin = 230 MHz IF

- SNR: 60.7 dBFS

- SFDR: 78 dBc

- Performance at fin = 700 MHz IF

- SNR: 58.9 dBFS

- SFDR: 73 dBc

- Receive Mode: 2x Decimation with Low Pass or

High Pass Filter - Feedback Mode: Burst Mode Output for Full

Bandwidth DPD Feedback

Description for the ADS54T02

The ADS54T02 is a high linearity dual channel 12-bit, 750 MSPS analog-to-digital converter (ADC) easing front end filter design for wide bandwidth receivers. The analog input buffer isolates the internal switching of the on-chip track-and-hold from disturbing the signal source as well as providing a high-impedance input. Two output modes are available for the output data – it can be decimated by two or the data can be output in burst mode. The burst mode output is designed specifically for DPD feedback applications where high resolution output data is available for a short period of time. Designed for high SFDR, the ADC has low-noise performance and outstanding spurious-free dynamic range over a large input-frequency range. The device is available in a 196pin BGA package and is specified over the full industrial temperature range (–40°C to 85°C).