JAJA750A november 2021 – december 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

3.4.3.2 内部 LDO と内部 DC/DC レギュレータ

F28004x には、内部 1.2V LDO 電圧レギュレータ (VREG) と内部 1.2V スイッチング・レギュレータ (DC/DC) が含まれています。このデバイスをシステムに実装する際、1.2V 電源レール用に内部 LDO と内部 DC/DC ソリューションのどちらを選択するかは、外部電源が望ましくない場合に設計上の重要な決定事項となります。DC/DC レギュレータは LDO よりも大幅に効率が高く、LDO レギュレータの効率が 30% であるのに対して DC/DC レギュレータの効率は 80% です。ただし、DC/DC ソリューションにはいくつかのトレードオフがあります。基板のレイアウトによっては、アナログ性能が低下する可能性があり、これは主に ADC に影響します。さらに、DC/DC には外部インダクタとコンデンサが必要であるため、部品コストが増加します。最後に、GPIO22 は VFBSW、GPIO23 は VSW により占有されるため、ボードの I/O 数が減少します。全体として、DC/DC 電圧レギュレータは効率的な電圧レギュレーションと低ノイズを必要とするシステム (スイッチングが MCU の外部にあるため) と、追加の部品コストが問題にならないシステムで便利です。

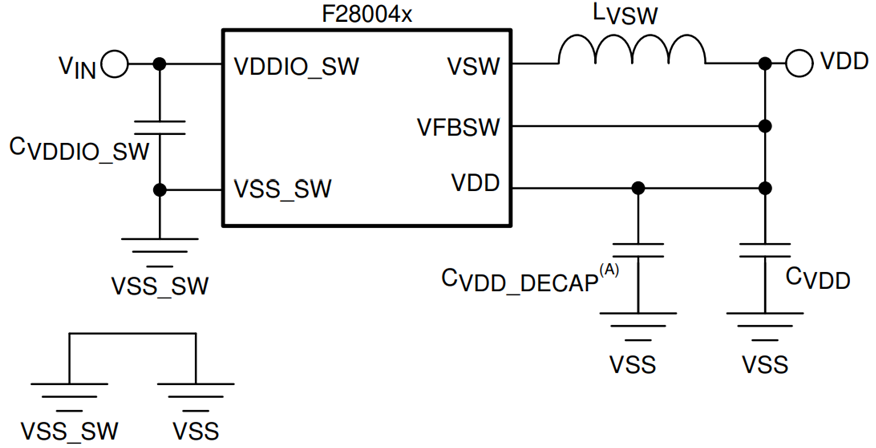

図 3-10 (『TMS320F28004x リアルタイム・マイクロコントローラ』データシートにも掲載) に、DC/DC レギュレータを使用するときに推奨される設計と必要な追加部品を示します。内部 DC/DC レギュレータの出力から VDD レールへの外部接続が必要であることに特に注意してください。

図 3-10 DC/DC レギュレータの回路図

図 3-10 DC/DC レギュレータの回路図