JAJA750A november 2021 – december 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

3.4.1 電源要件

デバイスに対して堅牢でノイズ耐性の高い電源を確実に供給するために重要なのは、すべての電源ピンにグランドへのデカップリング / バイパス・コンデンサを配置することです。これにより、システムの他の領域、特に低レベルのアナログ信号にノイズが拡散するのを制限できます。デカップリング・コンデンサは、フィルタおよび一時的なエネルギー・ストレージとして機能することで電源の電圧降下 / スパイクを最小限に抑え、デバイスの電源ソリューションの安定性を高めます。

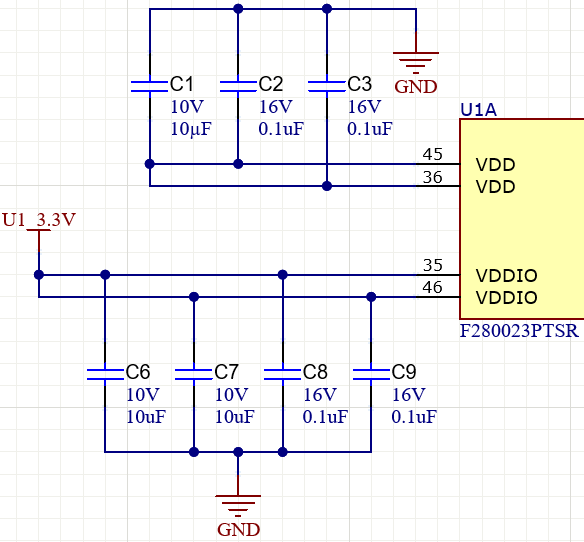

図 3-9 VDD ピンのデカップリング・コンデンサ

図 3-9 VDD ピンのデカップリング・コンデンサ(サポートされているデバイスで) 外部電圧レギュレータを使用して VDD に電源を供給する場合は、すべての VDD ピンを同じ 1.2V 電源レールに配線する必要があります。電圧供給を安定させるため、これらのピンにデカップリング・コンデンサが必要です。このデカップリング・コンデンサの値はデバイスによって異なります。CVDD に必要な値については、デバイスのデータシートを参照してください。VDDA および VDDIO 電源ピンにも、安定した電源電圧を維持するためにデカップリング・コンデンサが必要です。すべてのデバイスで、すべてのアナログ電源ピン (VDDA) に、アナログ・グランド (VSSA) に接続された 2.2µF 以上のデカップリング・コンデンサを配置する必要があります。デジタル I/O 電源 (VDDIO) には、上の図に示すように、各電源ピンの近くに 0.1µF 以上のデカップリング・コンデンサが必要です。一部のデバイスでは、すべてのピンで共有される追加のバルク・コンデンサ CVDDIO を配置することも推奨します。このバルク容量値は、使用するレギュレータによって異なります。該当するデバイスのデータシートを参照してください。

F28004x デバイスには、内部 DC/DC レギュレータ電源ピン (VDDIO_SW) が含まれていることに注意してください。このピンには、20µF のバルク入力容量が必要です。これには、2 個の 10µF コンデンサを並列接続することを推奨します。さらに、このピンは VDDIO ピンに接続し、両方のピンに同じ 3.3V ソースから電源を供給する必要があります。必要に応じて、絶縁用にフェライト・ビーズを使用することもできます。