JAJA750A november 2021 – december 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

3.3.3 内部および外部アナログ基準電圧

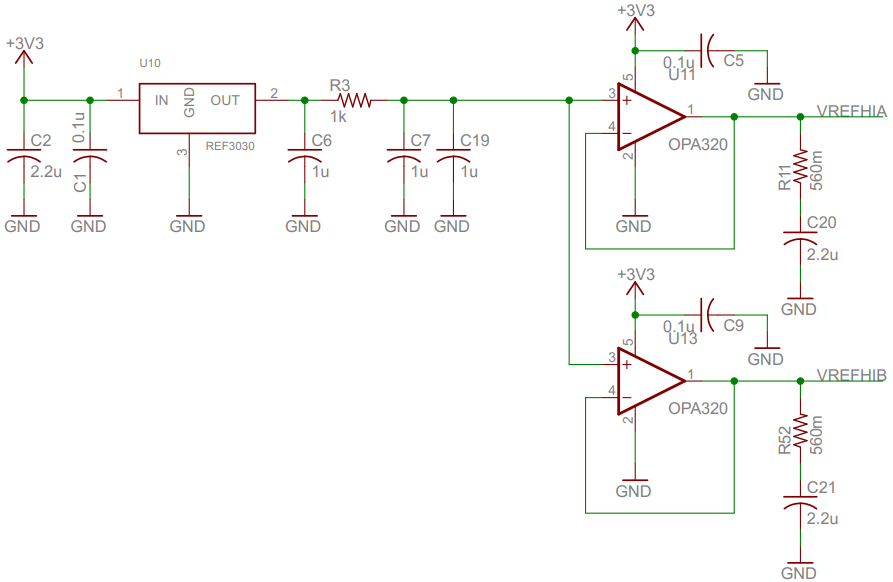

オンボードの ADC は、基準電圧として VREFHIx と VREFLOx を使用します。ほとんどのアプリケーションでは、内部基準電圧の性能で十分です。VREFHIx ピンの電圧は内部バンドギャップ基準電圧によって駆動され、1.65V の出力 (0V~3.3V) または 2.5V の出力 (0V~2.5V) を選択できます。実装するシステムの設計要件で高い精度が必要な場合は、代わりに外部基準電圧を使用できます。

内部基準電圧モードを使用する場合、VREFHI ピンにはデバイス自体から電圧が駆動されるため、追加の電圧源を配置しないでください。外部基準電圧モードでは、REF3030 や高速オペアンプなどの外部回路を使用して、高基準電圧ピンを外部から駆動します。この電圧は 2.4V~VDDA である必要があります。すべての場合に、ピンに 2.2µF のコンデンサを配置してください。

図 3-7 外部アナログ基準電圧用の基準電圧回路

図 3-7 外部アナログ基準電圧用の基準電圧回路