JAJA750A november 2021 – december 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

4.1.3 層のスタックアップ

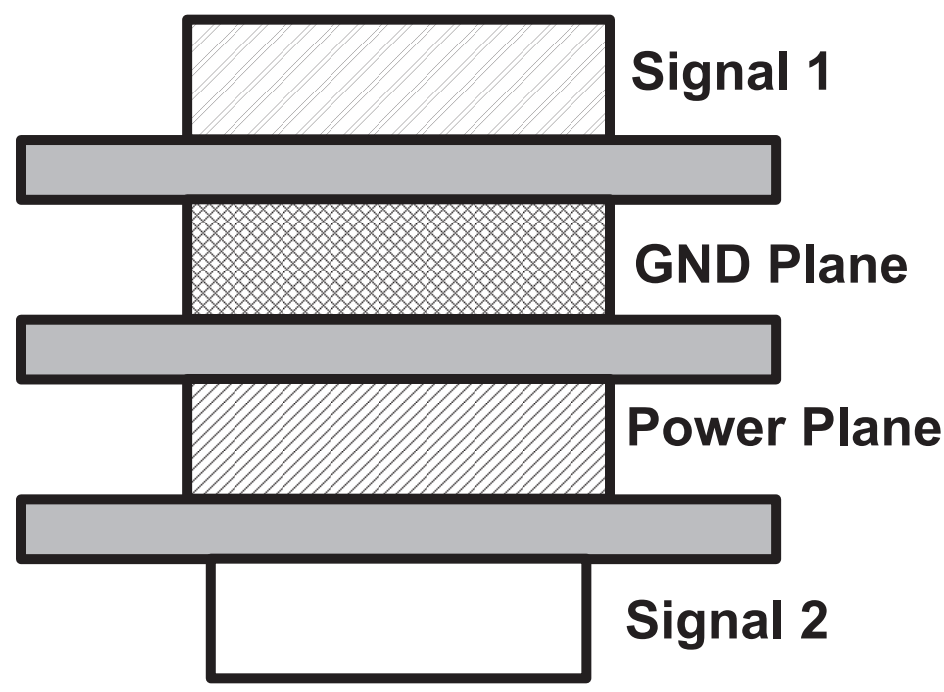

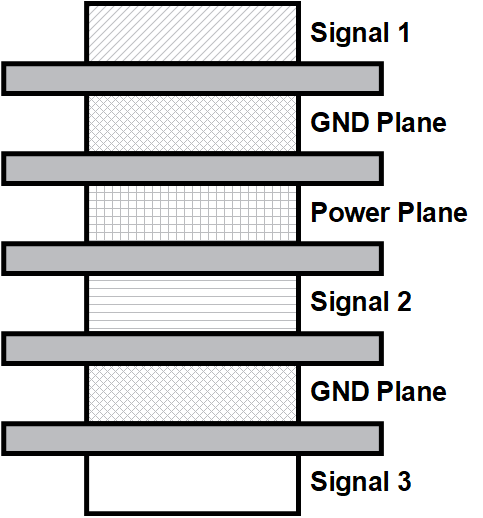

基板の層数と層のスタックアップ方式は、PCB 上に必要な接続の数と PCB の製造コストに応じて選択する必要があります。多くの場合、C2000 デバイスには 4 層以上のボードを選択するのが最適です。これにより、クリーンなグランド・プレーンと分離電源プレーンを含めることができます。次の図に、一般的な 4 層と 6 層の基板スタックアップ構成を示します。4 層基板スタックアップは、信号 / コンポーネント層、グランド・プレーン、分離電源プレーン (3.3V、1.2V など)、信号 / コンポーネント層で構成されています。6 層基板スタックアップは、信号 / コンポーネント層、グランド・プレーン、分離電源プレーン (3.3V、1.2V など)、信号層、別のグランド・プレーン、信号 / コンポーネント層で構成されています。

図 4-1 4 層基板スタックアップ構成

図 4-1 4 層基板スタックアップ構成 図 4-2 6 層基板スタックアップ構成

図 4-2 6 層基板スタックアップ構成