SPRAD57 August 2022 AM67 , AM67A , AM68 , AM68A , AM69 , AM69A , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4AEN-Q1 , TDA4AH-Q1 , TDA4AL-Q1 , TDA4AP-Q1 , TDA4APE-Q1 , TDA4VE-Q1 , TDA4VEN-Q1 , TDA4VH-Q1 , TDA4VL-Q1 , TDA4VM , TDA4VM-Q1 , TDA4VP-Q1 , TDA4VPE-Q1

2 Overview of Safety Mechanisms

For system level safety, robust hardware diagnostics for basic operations are layered with system and software diagnostic to meet random fault integrity metrics on the SoC. There are three basic categories of diagnostic coverage:

- Hardware safety

mechanisms: Once enabled, these mechanisms operate continuously.

- Examples of this include but are not limited to: SECDED ECC and Parity for memories and interconnect, PLL slip and loss of lock detection, over/under-voltage detection.

- Hardware + Software safety

mechanisms: These mechanisms depend on hardware but require periodic

software interaction to initiate or maintain the operation.

- Examples of this include but are not limited to: watchdog timers, CRC hardware support for checks of memory and registers, dual clock comparators.

- Software safety

mechanisms: These mechanisms are based on software performing some

test and checking the results.

- Examples of this include but are not limited to: Information redundancy techniques, transmission redundancy, software test of basic functionality. Implementation of these mechanisms are usually dependent on customer application and use case.

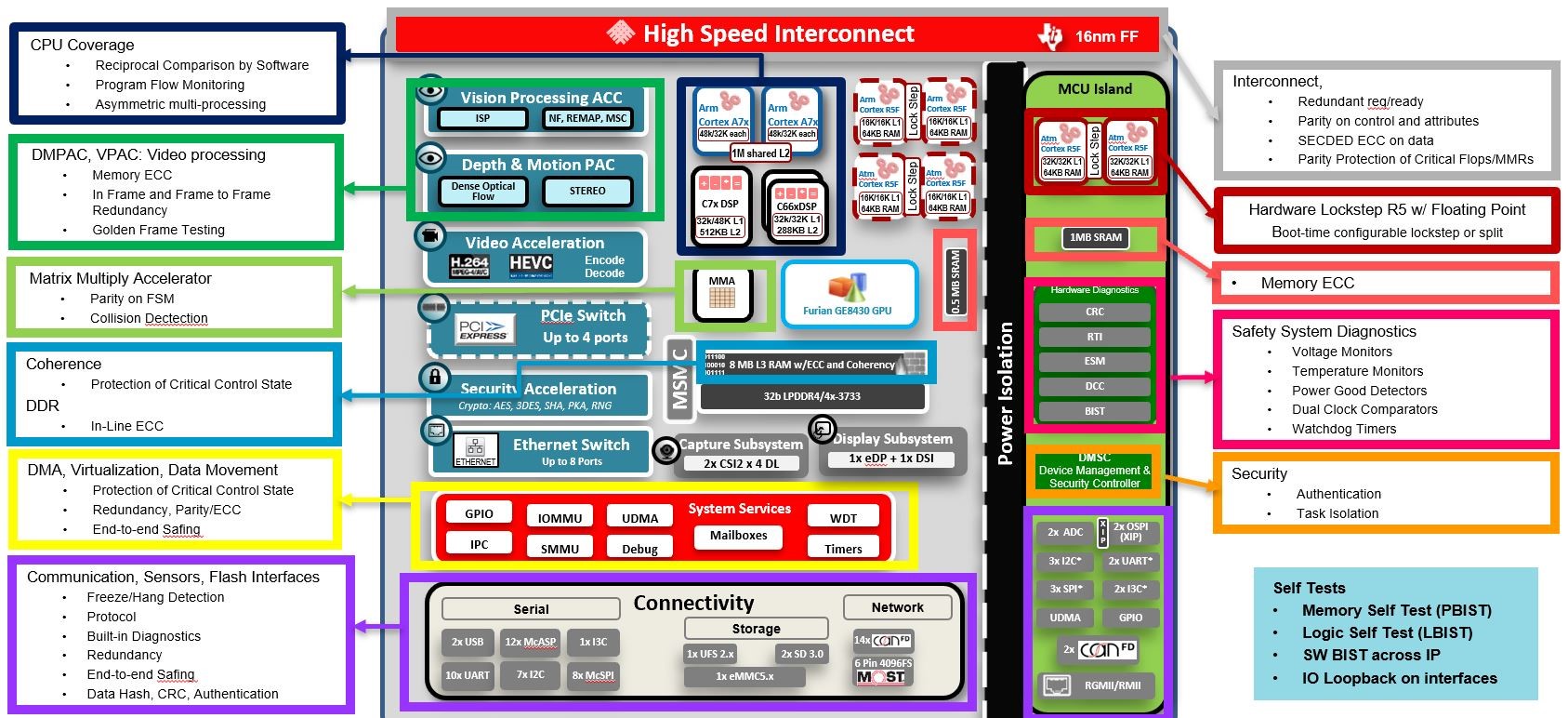

Figure 2 Select Diagnostics on TDA4VM

Figure 2 Select Diagnostics on TDA4VMFigure 2 demonstrates some safety mechanisms that can be implemented in the SoC (based of TDA4VM). This diagram is for informational purposes only and is not all inclusive. Please refer to SoC specific Safety Reference Manual for in depth descriptions of the diagnostics as well as for SOC specific modules and peripherals.