SPRACS8 May 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S

5 EEPROM Byte Read

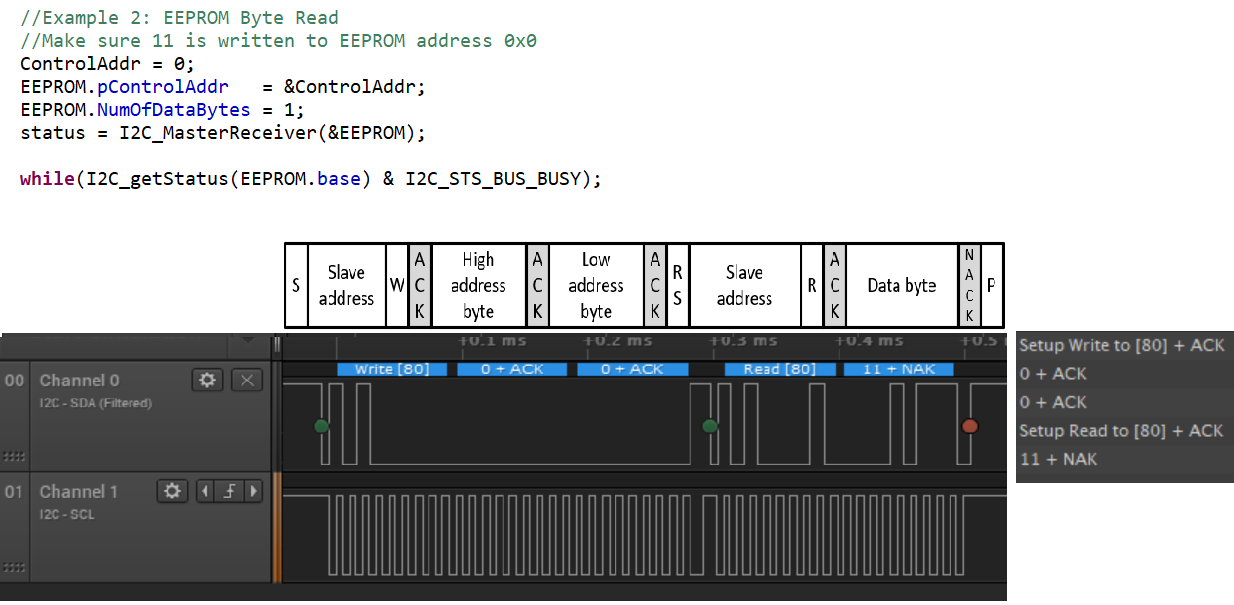

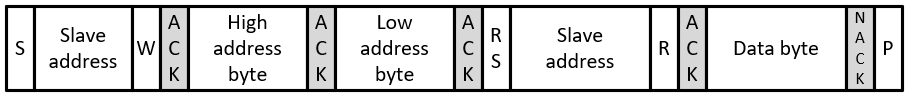

Figure 5-1 shows how EEPROM Byte Read protocol is defined in AT24C256. C2000 I2C is configured in Master Transmitter mode (I2CMDR.MST = 1, I2CMDR.TRX = 1) to transmit EEPROM address (both High address byte, Low address byte) and then C2000 I2C generates Repeated START condition in Master Receiver (I2CMDR.MST = 1, I2CMDR.TRX = 0) mode to receive a data byte from EEPROM.

Figure 5-1 EEPROM Byte Read

command

Figure 5-1 EEPROM Byte Read

commandCode flow:

- START condition + Transmit Slave address (0x50) + Write bit + ACK bit (from slave)

- Transmit EEPROM high address byte + ACK bit (from slave)

- Transmit EEPROM low address byte + ACK bit (from slave)

- Repeated START condition + Transmit Slave address (0x50) + Read bit + ACK bit (from slave)

- Receive data byte + ACK bit (from master)

- Generate STOP condition