SPRAD57 August 2022 AM67 , AM67A , AM68 , AM68A , AM69 , AM69A , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4AEN-Q1 , TDA4AH-Q1 , TDA4AL-Q1 , TDA4AP-Q1 , TDA4APE-Q1 , TDA4VE-Q1 , TDA4VEN-Q1 , TDA4VH-Q1 , TDA4VL-Q1 , TDA4VM , TDA4VM-Q1 , TDA4VP-Q1 , TDA4VPE-Q1

1 Jacinto™ 7 Safety Architecture Concepts

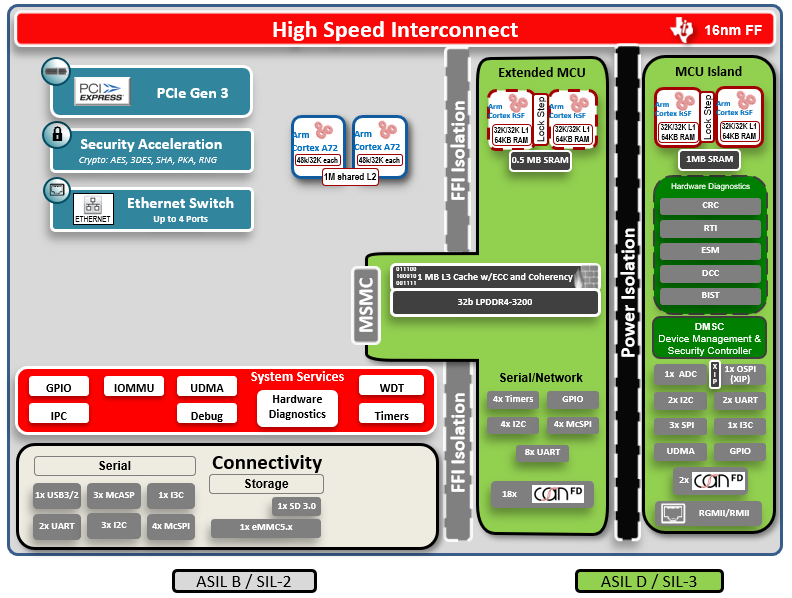

For a full architectural overview of the Jacinto devices please review the device technical reference manual of the respective SoC. Jacinto 7 SoCs target mixed criticality with a heterogeneous architecture and are scalable in terms performance, peripheral, and functional safety requirements. Each device within the Jacinto family will have a slightly different partitioning of safety components as well as safety targets, this is summarized within Table 1.

| Main Domain | MCU Domain | Extended MCU Island | Total ASIL-D/SIL-3 DMIPs | |

|---|---|---|---|---|

| DRA829/TDA4VM | ASIL-B/SIL-2 | ASIL-D/SIL-3 | N/A | Up to 2K |

| DRA821 | ASIL-B/SIL-2 | ASIL-D/SIL-3 | ASIL-D/SIL-3 | Up to 4K |

Figure 1 DRA821 Device

Figure 1 DRA821 Device