SPRUIQ4 May 2019 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S

- Introduction

- 1Getting Familiar With the Kit

-

2Hardware Overview

- 2.1 IDDK Evaluation Board

- 2.2 Functional Blocks

- 2.3 Processor Section

- 2.4 Control Processor Slot – H1

- 2.5 Expansion Processor Slots

- 2.6 Position Encoder Suite

- 2.7 Current Sensor Suite

- 2.8 Power Supplies and GND Plane Configurations

- 2.9 Rectifier and Inverter

- 2.10 DACs

- 2.11 Power Stage Disable Circuits

- 3Hardware Resource Mapping

2.11 Power Stage Disable Circuits

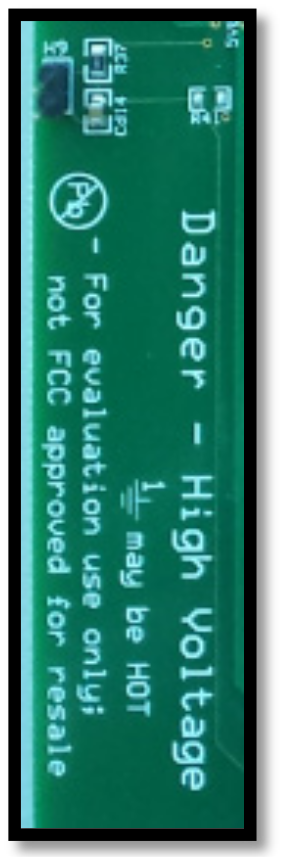

The power stage of the IDDK can be shut down using external digital signals. Figure 2-20 shows the external push-button interface employed to generate an emergency shutdown request using the H9 connector. This request can also be generated by overcurrent monitoring hardware, connectivity, and functional safety control processors on H7 and H8 connectors, respectively.

Figure 2-20 External Shutdown Signal Input

Figure 2-20 External Shutdown Signal Input Use appropriate protection logics in applications to safely disable the power stage.

WARNING

The board layout may not represent the optimal layout even though the best practices layout guidelines are followed.

Take care to adapt or modify the schematics and layout to meet your application requirements.