SPRUIS4E March 2022 – January 2024

- 1

- Jacinto7 J721E/DRA829/TDA4VM Evaluation Module (EVM)

- Trademarks

- 1Introduction

- 2J721E EVM Overview

- 3EVM User Setup/Configuration

-

4J721E EVM Hardware Architecture

- 4.1 J721E EVM Hardware Top level Diagram

- 4.2 J721E EVM Interface Mapping

- 4.3 I2C Address Mapping

- 4.4 GPIO Mapping

- 4.5 Power Supply

- 4.6 Reset

- 4.7 Clock

- 4.8 Memory Interfaces

- 4.9 MCU Ethernet Interface

- 4.10 QSGMII Ethernet Interface

- 4.11 PCIe Interface

- 4.12 USB Interface

- 4.13 CAN Interface

- 4.14 FPD Interface (Audio Deserializer)

- 4.15 FPD Panel Interface (DSI Video Serializer)

- 4.16 Display Serial Interface (DSI) FPC

- 4.17 Audio Interface

- 4.18 Display Port Interface

- 4.19 MLB Interface

- 4.20 I3C Interface

- 4.21 ADC Interface

- 4.22 RTC Interface

- 4.23 Apple Authentication Header

- 4.24 EVM Expansion Connectors

- 4.25 ENET Expansion Connector

- 4.26 CSI Expansion Connector

- 5Revision History

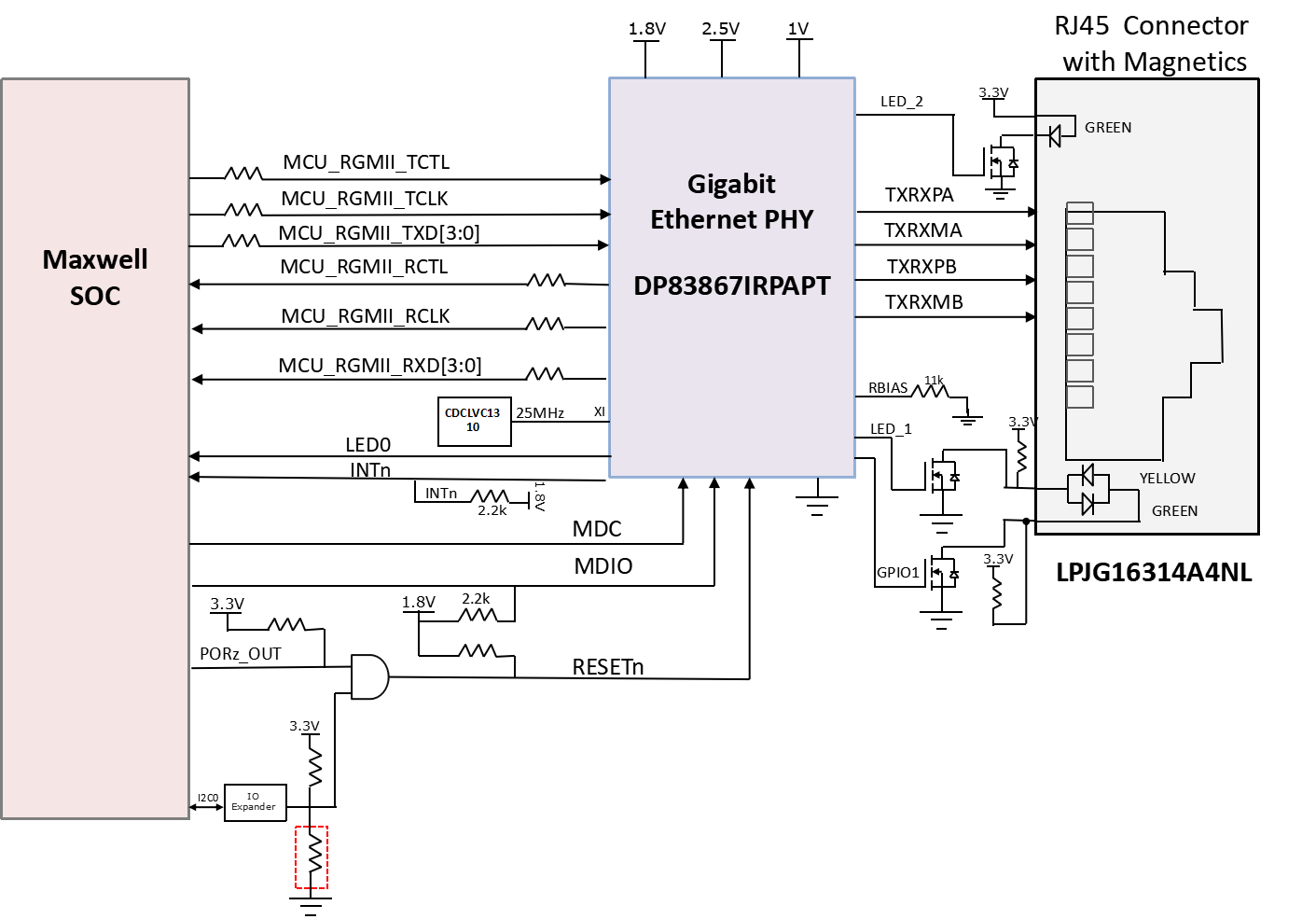

4.9 MCU Ethernet Interface

The EVM includes RGMII connection between DP83867ERGZT Gigabit Ethernet PHY and the MCU domain network subsystem (NSS) of the Processor. RJ45 connector (J35) with Integrated magnetics LPJG163144NL is used.

A reference clock of 25 Mhz will be generated onboard using a crystal to DP83867ERGZT.

Figure 4-15 MCU Gigabit Ethernet Block

Figure 4-15 MCU Gigabit Ethernet BlockThe I/O supply to the Ethernet PHY is set through selection Resistors R445 and R446 to support both 1.8 V and 3.3 V I/O level. The EVM is configured to 3.3 V I/O supply for MCU RGMII PHY I/O signals by default.