SLVAE87A December 2020 – October 2023 BQ79600-Q1 , BQ79612-Q1 , BQ79614-Q1 , BQ79616-Q1 , BQ79652-Q1 , BQ79654-Q1 , BQ79656-Q1

- 1

- Abstract

- Trademarks

- 1 NPN LDO Supply

- 2 AVDD, CVDD outputs and DVDD, NEG5, REFHP and REFHM

- 3 OTP Programming

- 4 Cell Voltage Sense (VCn) and Cell Balancing (CBn)

- 5 Bus Bar Support

- 6 TSREF

- 7 General Purpose Input-Output (GPIO) Configurations

- 8 Base and Bridge Device Configuration

- 9 Daisy-Chain Stack Configuration

- 10Multi-Drop Configuration

- 11Main ADC Digital LPF

- 12AUX Anti Aliasing Filter (AAF)

- 13Layout Guidelines

- 14BCI Performance

- 15Common and Differential Mode Noise

- 16Revision History

8.1.1 Power Mode Pings

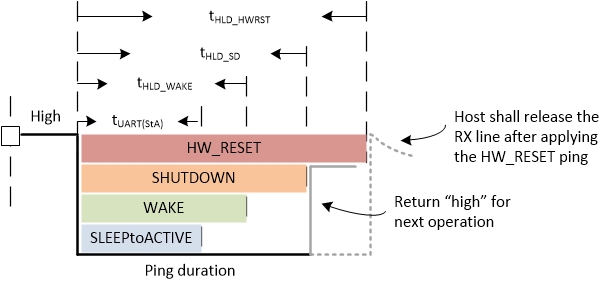

A ping is a specific high-low-high signal sent from MCU to the base device through the RX pin. Pings are used on the base device as only the base device is connected to the host from which the UART RX is accessible. The device detects the low pulse duration of the ping to differentiate between the different pings. There are total of 4 different pings as shown in Figure 8-3.

- a WAKE ping through RX pin

- a SHUTDOWN ping through RX pin

- a SLEEPtoACTIVE ping through RX pin

- a HW_RESET ping through RX pin

Figure 8-3 Communication Pings

Figure 8-3 Communication Pings