SLVAE87A December 2020 – October 2023 BQ79600-Q1 , BQ79612-Q1 , BQ79614-Q1 , BQ79616-Q1 , BQ79652-Q1 , BQ79654-Q1 , BQ79656-Q1

- 1

- Abstract

- Trademarks

- 1 NPN LDO Supply

- 2 AVDD, CVDD outputs and DVDD, NEG5, REFHP and REFHM

- 3 OTP Programming

- 4 Cell Voltage Sense (VCn) and Cell Balancing (CBn)

- 5 Bus Bar Support

- 6 TSREF

- 7 General Purpose Input-Output (GPIO) Configurations

- 8 Base and Bridge Device Configuration

- 9 Daisy-Chain Stack Configuration

- 10Multi-Drop Configuration

- 11Main ADC Digital LPF

- 12AUX Anti Aliasing Filter (AAF)

- 13Layout Guidelines

- 14BCI Performance

- 15Common and Differential Mode Noise

- 16Revision History

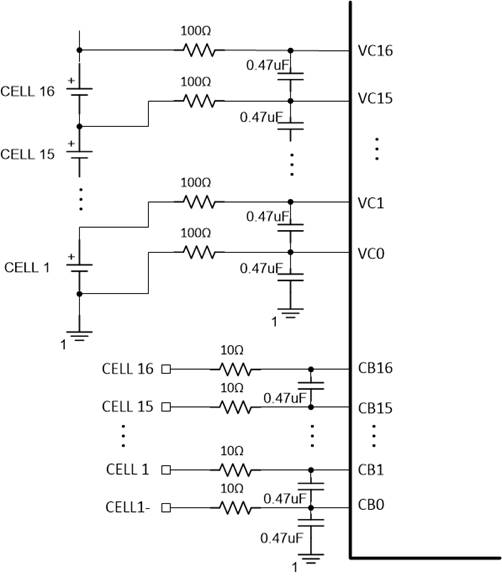

4.1 Cell Voltage Sense (VCn)

The VCn pins are the primary inputs for measuring the cell voltages. VC0 is the low side reference to the negative terminal of the bottom cell and VC16 is the high side reference to the positive terminal of the top cell.

The inputs should be connected to the cells using series resistors to limit current into the pins and protect the IC from system transients. When fewer than 16 cells are used on the BQ79616-Q1, the lower cells must be used in order. Unused cell connections can be found in the scenarios shown in Figure 4-1.

Recommended filter capacitor for VCn pins is 0.47 μF/16 V.

A 100 Ω is recommended as a series filter resistor for VCn pins. A 100 Ω is an optimized value to protect VCn pins from hotplug and provide better filtering. But if another value is considered other than 100 Ω, it should be simulated for selecting the optimized value for the system.