SLVAE87A December 2020 – October 2023 BQ79600-Q1 , BQ79612-Q1 , BQ79614-Q1 , BQ79616-Q1 , BQ79652-Q1 , BQ79654-Q1 , BQ79656-Q1

- 1

- Abstract

- Trademarks

- 1 NPN LDO Supply

- 2 AVDD, CVDD outputs and DVDD, NEG5, REFHP and REFHM

- 3 OTP Programming

- 4 Cell Voltage Sense (VCn) and Cell Balancing (CBn)

- 5 Bus Bar Support

- 6 TSREF

- 7 General Purpose Input-Output (GPIO) Configurations

- 8 Base and Bridge Device Configuration

- 9 Daisy-Chain Stack Configuration

- 10Multi-Drop Configuration

- 11Main ADC Digital LPF

- 12AUX Anti Aliasing Filter (AAF)

- 13Layout Guidelines

- 14BCI Performance

- 15Common and Differential Mode Noise

- 16Revision History

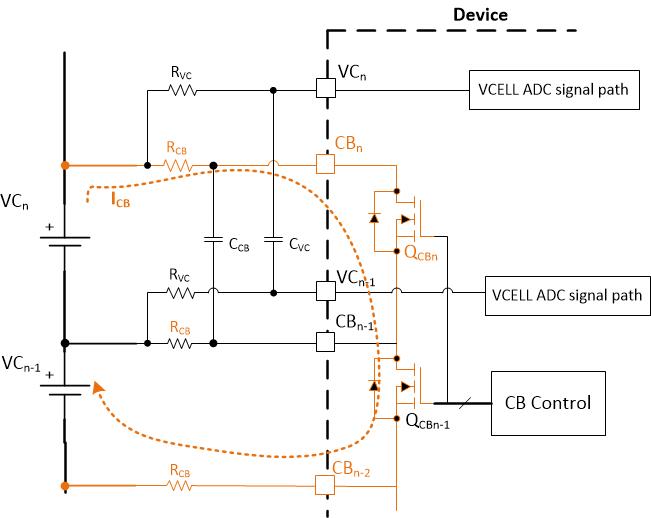

4.2.2 Adjacent Cell Balancing

Manual balancing control is configured by setting [AUTO_BAL] = 0. In manual balancing control mode, the host can enable two consecutive CBFETs, and a maximum of eight total CBFETs can be enabled (see Figure 4-4).

However, when two adjacent channels are enabled, the balancing current is twice as high or higher than the non-adjacent channel balancing current. The system designer shall take this into account if adjacent cell balancing is used. See Equation 4 to select the right adjacent cell balancing series resistor (RCB).

Figure 4-4 Adjacent Cell

Balancing

Figure 4-4 Adjacent Cell

Balancing