SLVAE87A December 2020 – October 2023 BQ79600-Q1 , BQ79612-Q1 , BQ79614-Q1 , BQ79616-Q1 , BQ79652-Q1 , BQ79654-Q1 , BQ79656-Q1

- 1

- Abstract

- Trademarks

- 1 NPN LDO Supply

- 2 AVDD, CVDD outputs and DVDD, NEG5, REFHP and REFHM

- 3 OTP Programming

- 4 Cell Voltage Sense (VCn) and Cell Balancing (CBn)

- 5 Bus Bar Support

- 6 TSREF

- 7 General Purpose Input-Output (GPIO) Configurations

- 8 Base and Bridge Device Configuration

- 9 Daisy-Chain Stack Configuration

- 10Multi-Drop Configuration

- 11Main ADC Digital LPF

- 12AUX Anti Aliasing Filter (AAF)

- 13Layout Guidelines

- 14BCI Performance

- 15Common and Differential Mode Noise

- 16Revision History

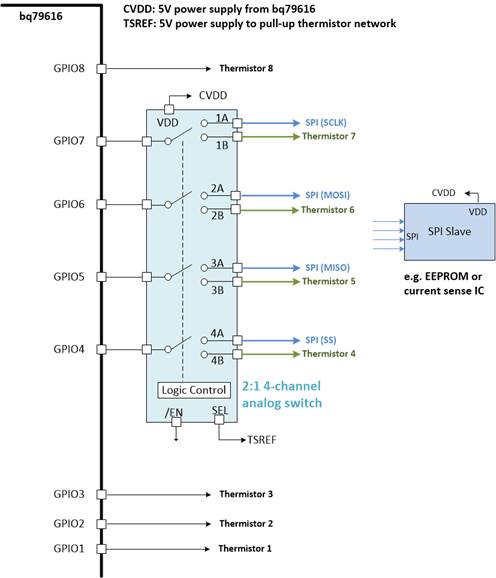

7.2.1 Support 8 NTC Thermistors With SPI Slave Device

A single 4-channel 2:1 switch can be use to switch between SPI and thermistor input. Single switches available at TI and can be powered from CVDD as shown in Figure 7-3.

Figure 7-3 8 NTC Thermistors With SPI

Slave Device

Figure 7-3 8 NTC Thermistors With SPI

Slave DeviceEnabling TSREF selects the “B” paths of the switch, which are all connected to NTCs for temperature measurement. Disabling TSREF disables all the thermistor networks, and also selects the “A” paths of the switch to allow SPI communication. This configuration has no impact to the temperature measurement diagnostic and will still have ASIL-D compliance on the temperature measurement.