SPRACM9B June 2019 – November 2020 F29H850TU , F29H859TU-Q1 , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- Trademarks

- 1 Introduction

- 2 Benefits of the TMS320F2838x MCU for High-Bandwidth Current Loop

- 3 Current Loops in Servo Drives

- 4 Outline of the Fast Current Loop Library

- 5 Fast Current Loop Evaluation

- 6 Incremental Build Level 1

- 7 Incremental Build Level 2

- 8 Incremental Build Level 3

- 9 Incremental Build Level 4

- 10Incremental Build Level 5

- 11Incremental Build Level 6

- 12Incremental Build Level 7

- 13Incremental Build Level 8

- 14References

- 15Revision History

11.6 Influence of Current Feedback SNR

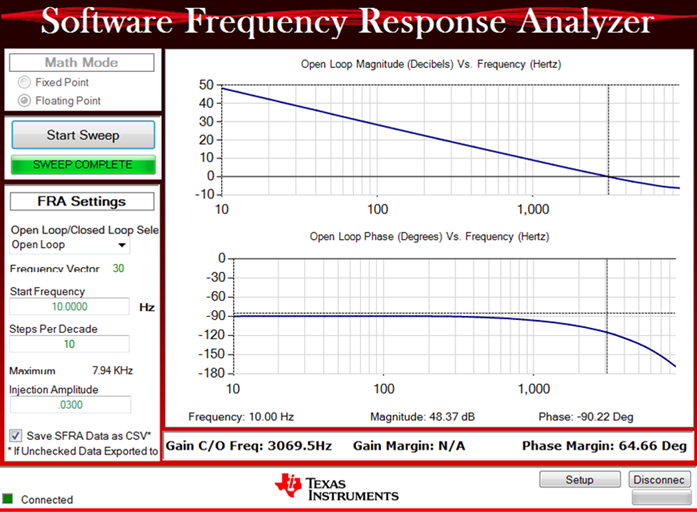

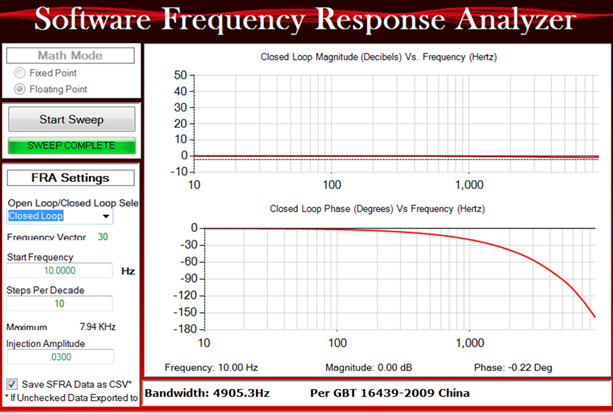

The fast current loop is a high bandwidth enabler. When the designed bandwidth is high, the loop gains can also be high. This pretty much ties the loop performance to the quality of current feedback. If the SNR of current feedback signal into the digital domain is poor, then the loop can be very audibly noisy as the controller tries to minimize the error. If the noise is bothersome, you may be required to reduce the bandwidth to avoid the audible noise. Therefore, for a higher bandwidth and higher performance, the feedbacks should be of higher SNR to get the frequency responses a shown in Figure 11-8 and Figure 11-9.

Figure 11-8 SFRA Open Loop Bode Plots of

the Current Loop - Current Feedback With High SNR

Figure 11-8 SFRA Open Loop Bode Plots of

the Current Loop - Current Feedback With High SNR Figure 11-9 SFRA Closed Loop Bode Plots of

the Current Loop - Current Feedback With High SNR

Figure 11-9 SFRA Closed Loop Bode Plots of

the Current Loop - Current Feedback With High SNR