SPRACM9B June 2019 – November 2020 F29H850TU , F29H859TU-Q1 , F29P329SM-Q1 , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- Trademarks

- 1 Introduction

- 2 Benefits of the TMS320F2838x MCU for High-Bandwidth Current Loop

- 3 Current Loops in Servo Drives

- 4 Outline of the Fast Current Loop Library

- 5 Fast Current Loop Evaluation

- 6 Incremental Build Level 1

- 7 Incremental Build Level 2

- 8 Incremental Build Level 3

- 9 Incremental Build Level 4

- 10Incremental Build Level 5

- 11Incremental Build Level 6

- 12Incremental Build Level 7

- 13Incremental Build Level 8

- 14References

- 15Revision History

8.1.1 From the Expressions Window

While running the motor in this build level and subsequent build levels, observe the variable fclLatencyInMicroSec in the Expressions window.

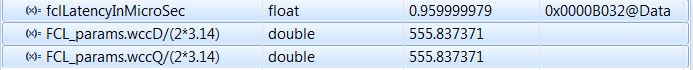

Figure 8-2 shows a snapshot of the Expressions window.

Figure 8-2 Expressions Window Snapshot For Latency

Figure 8-2 Expressions Window Snapshot For LatencyThis variable indicates the amount of time elapsed between the feedback sampling and PWM updating. The elapsed time, or latency, is computed based on the count of the EPWM timer right after the PWM update. The value shown here is more than the actual update time by a few clock cycles. Immediately after setting the runMotor flag to MOTOR_RUN and the motor begins to run, the latency time shows up as nearly 1.25 µs due to initial setup in the code. This amount of latency occurs at a time when the duty cycle is moderate and is therefore acceptable. After this period, you can refresh the latency time by setting fclClrCntr to 1. Regardless of SAMPLING_METHOD, latency remains the same for a given FCL_CNTLR. When FCL_CNTLR is a PI_CNTLR, the latency is about 0.96 µs compared to 0.98 µs with a CMPLX_CNTLR (see the following note).

- These times can be reduced further by around 0.1 µs range using code inline and other optimization techniques. Because the evaluation code is in library format, it has certain overheads.

- The sampling window for ADC is kept wide enough to ensure a cleaner signal acquisition. Depending on board layout and circuits feeding in to ADC channels, it may be possible to reduce this time window by nearly 60%.