SPRAD28 October 2022 AM2431 , AM2432 , AM2434 , AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM26C31 , AM26C31-EP , AM26C31C , AM26C31I , AM26C31M , AM26C32 , AM26C32-EP , AM26C32C , AM26C32M , AM26LS31 , AM26LS31M , AM26LS32A , AM26LS32AC , AM26LS32AM , AM26LS33A , AM26LS33A-SP , AM26LS33AM , AM26LV31 , AM26LV31E , AM26LV31E-EP , AM26LV32 , AM26LV32E , AM26LV32E-EP , AM26S10 , AM2732 , AM2732-Q1

- Abstract

- Trademarks

- 1 Building for Debug

- 2 Code Composer Studio Stop-Mode Debugging

- 3 Debug Logging

- 4 Multi-Core Debug

- 5 Debugging Arm Cortex-R5 Exceptions

- 6 Debugging Arm Cortex-M4 Exceptions

- 7 Debugging Memory

- 8 Debugging Boot

- 9 Debugging Real-Time Control Loops

- 10E2E Support Forums

6.2.4 Control Registers

The System control block (SCB) provides system implementation information, and system control. This includes configuration, control, and reporting of the system exceptions. Some of its registers are used to control fault exceptions:

- CCR - Configuration and Control Register, controls the behavior of the UsageFault for divideby-zero and unaligned memory accesses

- SHP - System Handler Priority Registers, control the exception priority

- SHCRS - System Handler Control and State Register, enables the system handlers, and indicates the pending status of the BusFault, MemManage fault, and SVC exceptions

| Register | Address | Description |

|---|---|---|

| CCR | 0xE000ED14 | Configuration and Control Register: contains enable bits for trapping of divide-by-zero and unaligned accesses with the UsageFault. |

| SHP | 0xE000ED18 | System Handler Priority registers: control the priority of exception handlers. |

| SHCRS | 0xE000ED24 | The SHCSR enables the

system handlers, and indicates:

|

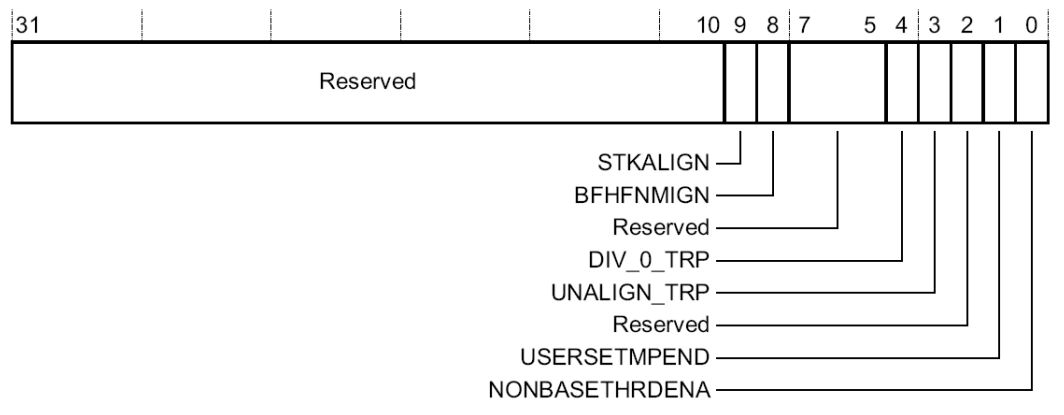

Figure 6-2 CCR - Configuration and

Control Register

Figure 6-2 CCR - Configuration and

Control RegisterThe following bits of the CCR register control the behavior of the Usage Fault:

DIV_0_TRP: Enables UsageFault when the processor executes an SDIV or UDIV instruction with a divisor of 0:

- When '0' = do not trap divide by 0; a divide by 0 returns a quotient of 0.

- When '1' = trap divide by 0.

UNALIGN_TRP: Enable UsageFault when a memory access to unaligned addresses are performed:

- When '0' = do not trap unaligned halfword and word accesses

- When '1' = trap unaligned halfword and word accesses; an unaligned access generates a UsageFault