SPRAD28 October 2022 AM2431 , AM2432 , AM2434 , AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P2-Q1 , AM263P4 , AM263P4-Q1 , AM26C31-EP , AM26C31M , AM26C32-EP , AM26C32C , AM26C32M , AM26LS31M , AM26LS32AM , AM26LS33A-SP , AM26LS33AM , AM26LV31E-EP , AM26LV32E-EP , AM26S10 , AM2732 , AM2732-Q1

- Abstract

- Trademarks

- 1 Building for Debug

- 2 Code Composer Studio Stop-Mode Debugging

- 3 Debug Logging

- 4 Multi-Core Debug

- 5 Debugging Arm Cortex-R5 Exceptions

- 6 Debugging Arm Cortex-M4 Exceptions

- 7 Debugging Memory

- 8 Debugging Boot

- 9 Debugging Real-Time Control Loops

- 10E2E Support Forums

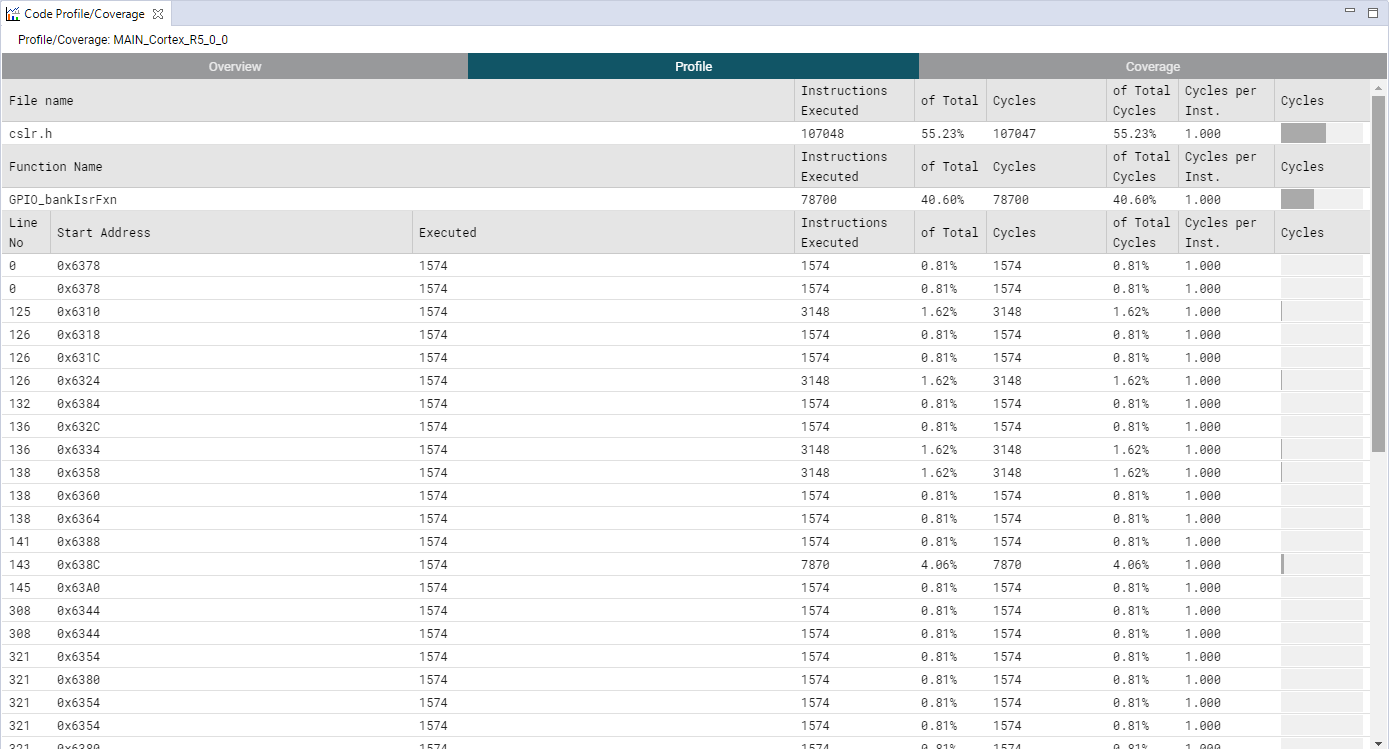

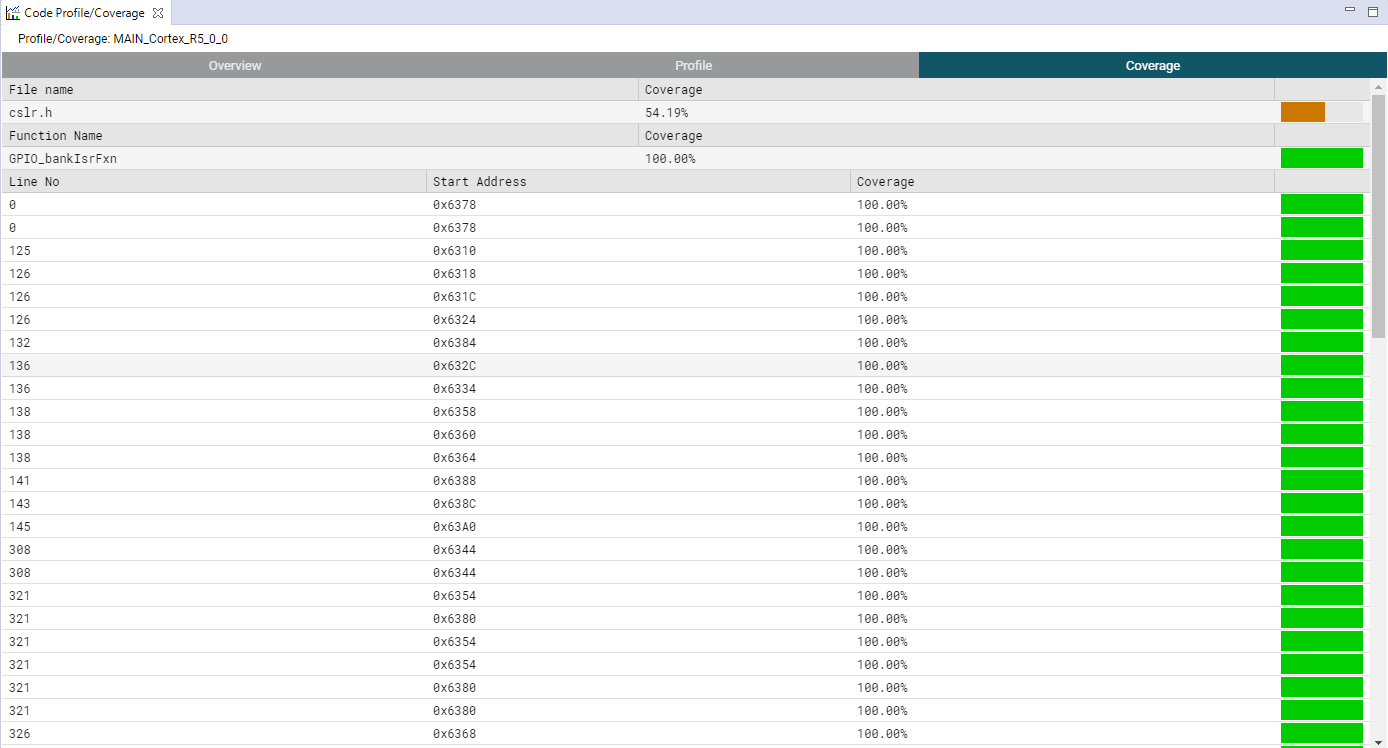

9.2 Code Profile / Coverage

Sitara MCU devices support code coverage that is particularly suited for embedded applications. In addition to being generally useful for thorough application development, code coverage is required by internal and external developers in the Industrial and Automotive markets for Functional Safety.

In order to open the Code Coverage tool, click on Tools->Code Analysis->Code Profile / Coverage.

The code coverage and profiling shows you how often a function / file is called, how much code of the file was executed, how many instructions and cycles it took and more.